Analog To Digital – Convertitori SAR, Flash e ibridi: Architetture ad Alta Efficienza e Alta Velocità

Lorenzo Martini, 16/04/25

Introduzione: Due Approcci Divergenti alla Conversione Analogico-Digitale

Nel vasto panorama delle tecnologie di conversione analogico-digitale, le architetture SAR (Successive Approximation Register) e Flash rappresentano due filosofie profondamente diverse, quasi antitetiche, che rispondono a esigenze applicative specifiche. Da un lato, il convertitore SAR incarna l’approccio sequenziale ed efficiente, ottimizzando l’utilizzo delle risorse hardware attraverso un algoritmo iterativo. Dall’altro, il convertitore Flash rappresenta la soluzione “brute force”, privilegiando la velocità assoluta attraverso la massiccia parallelizzazione.

Queste due architetture dominano segmenti di mercato complementari e la loro comprensione approfondita è fondamentale per progettisti e decision-maker chiamati a selezionare la tecnologia di conversione più appropriata per applicazioni specifiche. Nel contesto attuale, caratterizzato dalla crescente importanza dell’elaborazione dei segnali in tempo reale e dall’espansione dell’Internet delle Cose (IoT), queste architetture hanno assunto un ruolo ancora più strategico nell’ecosistema dell’elettronica moderna.

In questo articolo, esploreremo in dettaglio i principi operativi, i parametri prestazionali, i vantaggi e i limiti di entrambe le architetture, fornendo un quadro comparativo che evidenzi i rispettivi domini applicativi ottimali.

Convertitori ad Approssimazioni Successive (SAR): L’Algoritmo Binario al Servizio dell’Efficienza

Il convertitore SAR implementa un algoritmo di ricerca binaria per determinare, bit per bit, la rappresentazione digitale che meglio approssima il valore analogico di ingresso. Come in una partita di indovinelli in cui ad ogni domanda si dimezza lo spazio di ricerca, il convertitore SAR riduce progressivamente l’incertezza sul valore analogico.

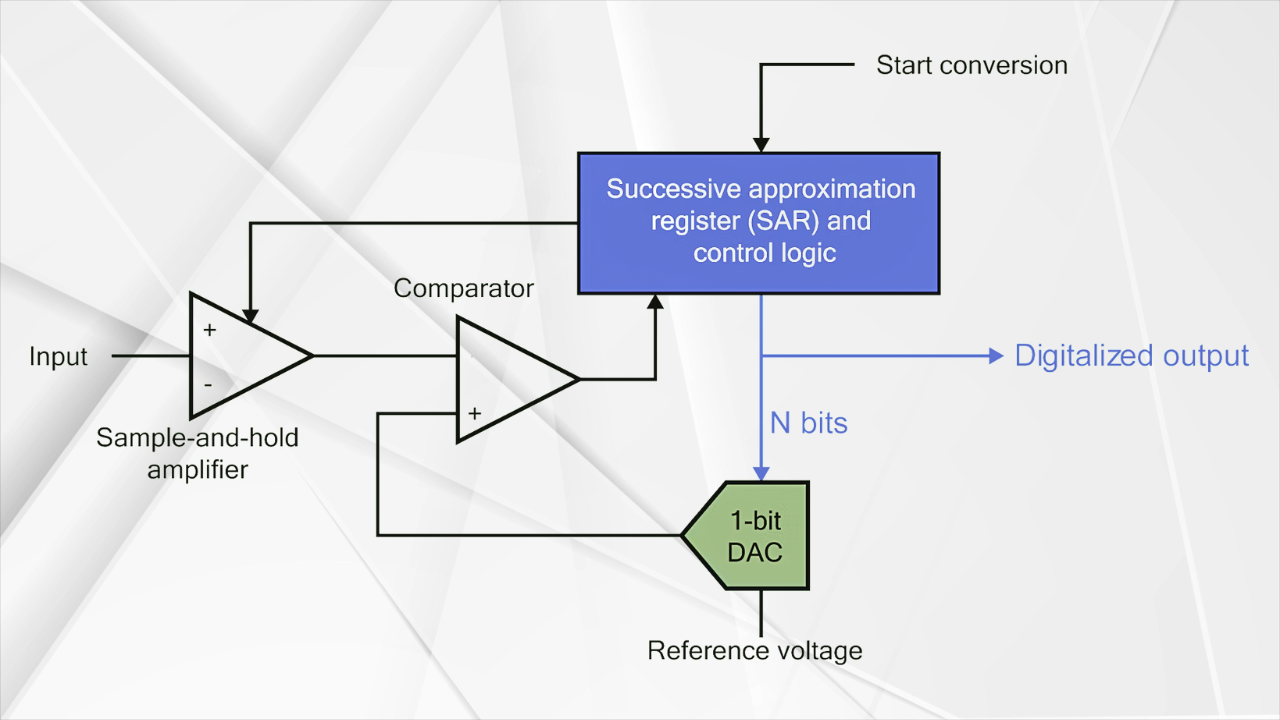

L’architettura di base di un ADC SAR comprende quattro elementi fondamentali:

- Circuito di Sample-and-Hold: Campiona e mantiene stabile il segnale analogico durante l’intero processo di conversione.

- Comparatore: Confronta il segnale analogico con l’output del DAC interno.

- Registro SAR: Memorizza il risultato progressivo della conversione e implementa la logica dell’algoritmo di approssimazione.

- Convertitore Digitale-Analogico (DAC): Converte il valore digitale corrente in un segnale analogico per il confronto. riduce progressivamente l’incertezza sul valore analogico.

Algoritmo di Conversione

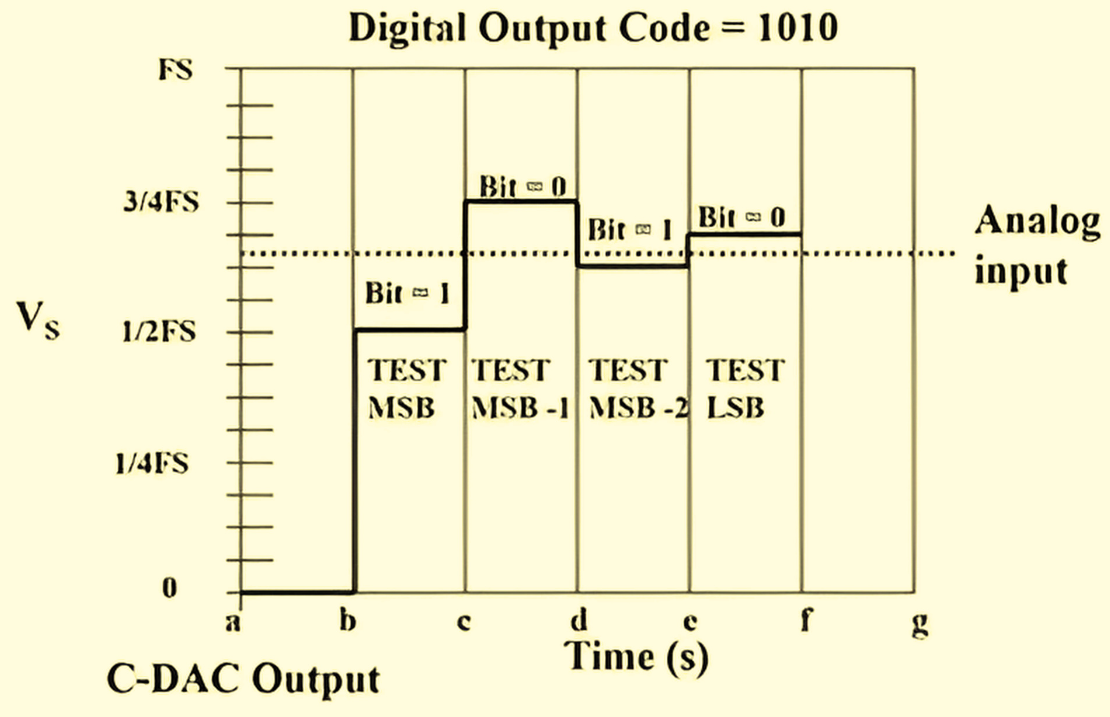

L’algoritmo SAR opera secondo una sequenza ben definita:

- Il circuito Sample-and-Hold acquisisce e blocca il valore analogico di ingresso (Vin).

- Il registro SAR viene inizializzato impostando il bit più significativo (MSB) a 1 e tutti gli altri a 0.

- Il valore corrente del registro viene inviato al DAC, che produce un segnale analogico corrispondente (VDAC).

- Il comparatore confronta VDAC con Vin:

- Se VDAC > Vin, il bit corrente viene azzerato

- Se VDAC ≤ Vin, il bit corrente rimane a 1

- L’algoritmo passa al bit successivo, impostandolo a 1.

- I passaggi 3-5 vengono ripetuti fino all’elaborazione dell’ultimo bit (LSB).

- Al termine, il registro SAR contiene la rappresentazione digitale del valore analogico.

Questo processo richiede esattamente N cicli di clock per un convertitore a N bit, indipendentemente dal valore di ingresso.

Implementazioni Avanzate

Le implementazioni moderne di ADC SAR incorporano numerosi raffinamenti rispetto all’architettura di base, migliorando significativamente le prestazioni:

DAC a Capacità Commutate: Sostituisce il tradizionale DAC a resistori con una rete di condensatori, offrendo vantaggi in termini di accuratezza, consumo e area. Questa implementazione sfrutta la precisione degli accoppiamenti capacitivi nei processi CMOS moderni.

Tecniche di Calibrazione Digitale: Permettono di compensare gli errori di mismatch dei componenti, migliorando parametri come INL, DNL e offset. Queste tecniche possono essere implementate sia in fabbrica che in modo dinamico durante il funzionamento.

Architetture Split-Capacitor: Riducono l’area e il consumo del DAC dividendo la rete capacitiva in sezioni, con conseguente riduzione esponenziale della capacità totale richiesta.

Campionamento Differenziale: Migliora l’immunità al rumore e alle interferenze utilizzando ingressi differenziali anziché single-ended.

Caratteristiche Prestazionali e Limitazioni

I convertitori SAR offrono un eccellente equilibrio tra vari parametri prestazionali:

Risoluzione: Tipicamente tra 8 e 16 bit, con implementazioni avanzate che possono raggiungere i 18-20 bit.

Velocità: Da poche centinaia di kSPS fino a decine di MSPS nelle implementazioni più veloci. La natura sequenziale dell’algoritmo pone un limite intrinseco alla velocità massima.

Consumo Energetico: Generalmente molto efficiente, con figure di merito (FoM) che possono raggiungere pochi femtoJoule per conversione, ideale per applicazioni a bassa potenza.

Accuratezza: Buona linearità e bassa distorsione, particolarmente nelle implementazioni avanzate con tecniche di calibrazione.

Area di Silicio: Relativamente compatta, con dimensioni che crescono linearmente (e non esponenzialmente) con la risoluzione.

La principale limitazione dell’architettura SAR risiede nella velocità massima di conversione, vincolata dal numero di cicli di clock necessari per completare l’algoritmo.

Caso Applicativo: Sistema di Monitoraggio Multi-Parametrico in Ambito Biomedicale

Un esempio concreto di applicazione ideale per un convertitore SAR è rappresentato da un sistema di monitoraggio multi-parametrico per applicazioni biomedicali.

Scenario: Un dispositivo indossabile per il monitoraggio continuo di parametri vitali (ECG, temperatura corporea, ossimetria, pressione) deve operare a bassa potenza per garantire lunga autonomia, mantenendo al contempo precisione sufficiente per l’affidabilità diagnostica.

Implementazione:

- Convertitore SAR a 12 bit con frequenza di campionamento configurabile (250 SPS – 2 kSPS)

- Front-end analogico con amplificatore a guadagno programmabile per adattarsi ai diversi segnali

- Multiplexer analogico per gestire fino a 8 canali di ingresso

Modalità di risparmio energetico con wake-up automatico su eventi

Modalità di risparmio energetico con wake-up automatico su eventi

Prestazioni:

- Consumo energetico: 30 μW per canale a 1 kSPS

- Risoluzione effettiva (ENOB): 11.2 bit

- Tempo di conversione: 8 μs per campione

- Tensione di riferimento: Interna (1.25V) con stabilità termica < 10 ppm/°C

Questa soluzione consente di monitorare continuamente i parametri vitali con un’autonomia di oltre una settimana utilizzando una piccola batteria al litio, mantenendo la precisione necessaria per identificare anomalie clinicamente significative.

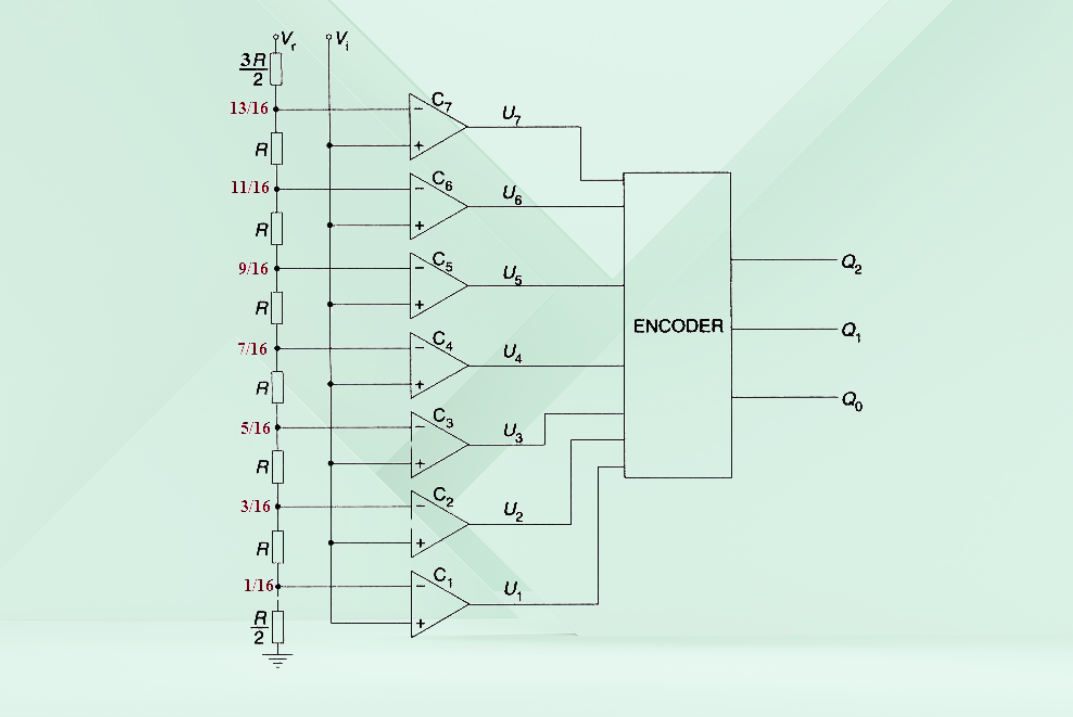

Convertitori Flash: L’Architettura della Massima Velocità

Il convertitore Flash (o parallelo) rappresenta l’approccio più diretto alla conversione analogico-digitale, implementando simultaneamente tutti i confronti necessari per determinare il codice digitale finale.

L’architettura di base di un ADC Flash comprende tre elementi fondamentali:

- Rete di Resistori di Riferimento: Genera 2N-1 livelli di tensione di riferimento uniformemente distribuiti tra il minimo e il massimo della scala.

- Array di Comparatori: Ogni comparatore confronta simultaneamente il segnale di ingresso con uno dei livelli di riferimento.

- Encoder di Priorità: Converte il pattern degli output dei comparatori nel formato binario finale.

Processo di Conversione

Il processo di conversione in un ADC Flash è concettualmente semplice e diretto:

- Il segnale analogico di ingresso viene simultaneamente applicato a tutti i comparatori.

- Ogni comparatore genera un output binario in base al confronto con il proprio livello di riferimento:

- Se Vin > Vref(i), l’output è 1

- Se Vin ≤ Vref(i), l’output è 0

- Gli output dei comparatori formano un “codice termometrico” in cui tutti i comparatori fino a un certo punto restituiscono 1, e tutti quelli successivi restituiscono 0.

- L’encoder di priorità converte il codice termometrico nella corrispondente rappresentazione binaria.

L’intera conversione avviene essenzialmente in un unico ciclo di clock, limitata solo dai ritardi di propagazione attraverso i comparatori e l’encoder.

Implementazioni Avanzate

Le implementazioni moderne di ADC Flash incorporano numerose ottimizzazioni per migliorare le prestazioni e ridurre le problematiche intrinseche:

Architetture a Interpolazione: Riducono il numero di comparatori fisici utilizzando tecniche di interpolazione tra nodi adiacenti, diminuendo significativamente area e consumo.

Tecniche di Media e Folding: Consentono di ridurre ulteriormente la complessità hardware mantenendo prestazioni comparabili.

Calibrazione Dinamica: Compensa le variazioni di offset dei comparatori che possono causare errori di monotonia e linearità.

Architetture Differenziali: Migliorano l’immunità al rumore e alle variazioni di modo comune.

Caratteristiche Prestazionali e Limitazioni

I convertitori Flash offrono prestazioni di velocità ineguagliabili, ma con compromessi significativi:

Velocità: Estremamente elevata, da centinaia di MSPS fino a diversi GSPS nelle implementazioni più avanzate, rendendo questa architettura insuperabile per applicazioni ad altissima frequenza.

Risoluzione: Tipicamente limitata a 8 bit o meno, con rare implementazioni che raggiungono i 10 bit a costo di una significativa complessità.

Consumo Energetico: Molto elevato, con figure di merito (FoM) generalmente nell’ordine di pJ/conversione o superiori, limitando l’applicabilità in sistemi a bassa potenza.

Area di Silicio: Cresce esponenzialmente con la risoluzione, rendendo impraticabili implementazioni ad alta risoluzione. Un ADC Flash a 8 bit richiede 255 comparatori, mentre uno a 10 bit ne richiede 1023.

Complessità di Layout: L’elevato numero di comparatori identici richiede particolare attenzione al layout per garantire prestazioni uniformi e minimizzare errori sistematici.

Le principali limitazioni dell’architettura Flash risiedono nel consumo energetico elevato, nell’area di silicio crescente esponenzialmente con la risoluzione, e nelle sfide di implementazione per garantire uniforme comportamento di tutti i comparatori.

Caso Applicativo: Ricevitore Digitale per Comunicazioni Ottiche ad Alta Velocità

Un esempio emblematico di applicazione ideale per un convertitore Flash è rappresentato da un ricevitore digitale per sistemi di comunicazione ottica.

Scenario: Un sistema di comunicazione ottica operante a 100 Gbps utilizza una modulazione PAM-4 (Pulse Amplitude Modulation a 4 livelli), richiedendo un ricevitore in grado di campionare il segnale a 50+ GSample/s con risoluzione sufficiente a discriminare i quattro livelli di ampiezza.

Implementazione:

- Convertitore Flash a 6 bit con frequenza di campionamento di 56 GSPS

- Front-end analogico con amplificatore a banda ultra-larga (>25 GHz)

- Equalizzatore adattivo implementato in digitale post-conversione

- Tecnologia di processo avanzata (28nm o inferiore) per gestire le frequenze di clock

Prestazioni:

- Banda analogica: >28 GHz

- ENOB a Nyquist: 4.8 bit (sufficiente per la modulazione PAM-4)

- Consumo: 1.8W (accettabile considerando l’applicazione ad alte prestazioni)

- Jitter di apertura: <150 fs RMS

Questa soluzione consente di implementare un ricevitore completamente digitale per sistemi di comunicazione ottica, spostando la maggior parte dell’elaborazione del segnale nel dominio digitale e aumentando la flessibilità del sistema attraverso tecniche di elaborazione programmabili.

Analisi Comparativa: Quando Scegliere SAR vs Flash

La scelta tra architetture SAR e Flash deve basarsi su un’attenta analisi dei requisiti applicativi e dei relativi compromessi. La seguente tabella offre un confronto diretto delle principali caratteristiche:

| Parametro | ADC SAR | ADC Flash |

|---|---|---|

| Velocità | Media (fino a ~20 MSPS) | Molto alta (fino a GSPS) |

| Risoluzione | Alta (8-16 bit, fino a 20) | Bassa (tipicamente 4-8 bit) |

| Consumo energetico | Basso (fJ/conversione) | Alto (pJ/conversione) |

| Area di silicio | Moderata, cresce linearmente | Grande, cresce esponenzialmente |

| Complessità circuitale | Media | Alta |

| Latenza | Media (N cicli per N bit) | Molto bassa (pipeline singolo stadio) |

| Drift termico | Moderato | Significativo |

| Immunità al rumore | Buona | Moderata |

Dominio Applicativo Ottimale: SAR

I convertitori SAR rappresentano la scelta ideale quando:

- L’efficienza energetica è prioritaria

- Dispositivi alimentati a batteria

- Sistemi di energy harvesting

- Reti di sensori wireless

- La risoluzione è più importante della velocità

- Strumentazione di precisione

- Acquisizione dati multicanale

- Sistemi di controllo industriale

- Le risorse di silicio sono limitate

- Sistemi integrati a basso costo

- Applicazioni IoT ad alta densità di integrazione

- Dispositivi indossabili

Esempio applicativo: Un sistema di monitoraggio ambientale distribuito con centinaia di nodi alimentati a batteria richiede convertitori efficienti energeticamente. L’implementazione con ADC SAR a 12 bit operanti a 10 kSPS consente di ottenere una risoluzione sufficiente per le misurazioni ambientali (temperatura, umidità, qualità dell’aria) con un consumo inferiore a 50 μW per canale. Questo permette di realizzare nodi sensore con autonomia di anni utilizzando batterie standard o tecniche di energy harvesting.

Dominio Applicativo Ottimale: Flash

I convertitori Flash sono la scelta ottimale quando:

- La velocità è il parametro critico

- Oscilloscopi digitali

- Radar e sistemi di difesa

- Comunicazioni digitali ad alta velocità

- La latenza deve essere minima

- Sistemi di controllo in loop

- Analizzatori di spettro in tempo reale

- Sistemi di trigger ad alta velocità

- Il consumo energetico non è un vincolo primario

- Apparecchiature da laboratorio

- Infrastrutture di rete

- Sistemi con alimentazione di rete

Esempio applicativo: Un sistema radar per applicazioni automotive richiede l’elaborazione di segnali RF riflessi con minima latenza per identificare ostacoli e veicoli in rapido movimento. Un ADC Flash a 8 bit operante a 1 GSPS consente di digitalizzare direttamente il segnale IF dopo il mixer, permettendo l’implementazione di algoritmi di elaborazione avanzati in FPGA o DSP. La bassa latenza dell’ADC Flash è cruciale per garantire tempi di risposta adeguati in scenari di sicurezza critica come la frenata automatica d’emergenza.

Architetture Ibride: Il Meglio di Entrambi i Mondi

Le limitazioni intrinseche delle architetture pure hanno portato allo sviluppo di approcci ibridi che combinano elementi di diverse topologie per ottenere compromessi prestazionali più favorevoli.

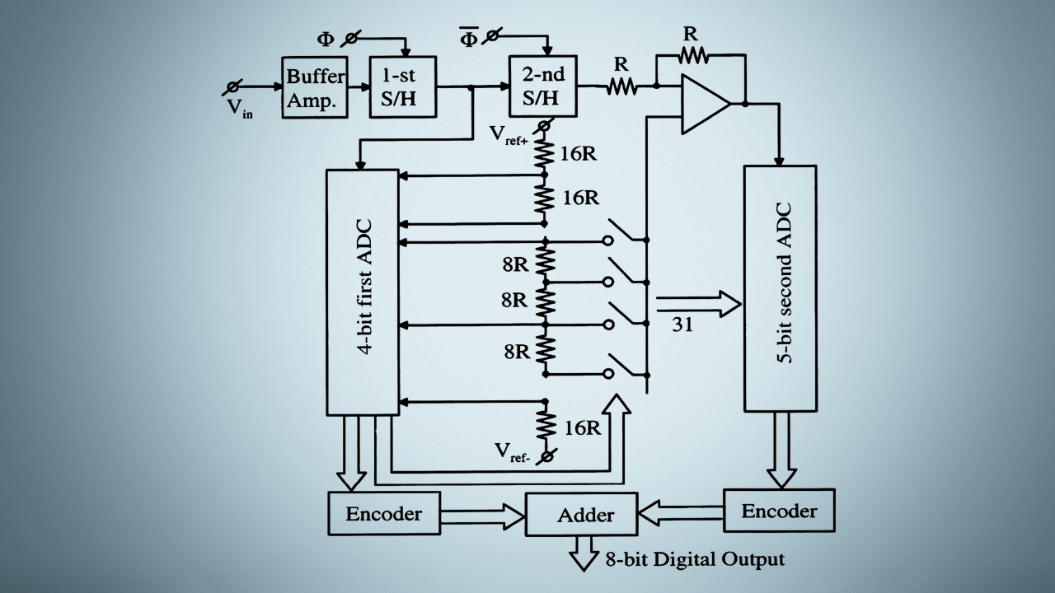

[FIGURA 16: Schema a blocchi di architetture ibride, mostrando in particolare: (a) ADC Flash a due stadi, (b) ADC Half-Flash, e (c) ADC Folding, con indicazione dei vantaggi rispetto alle architetture pure]

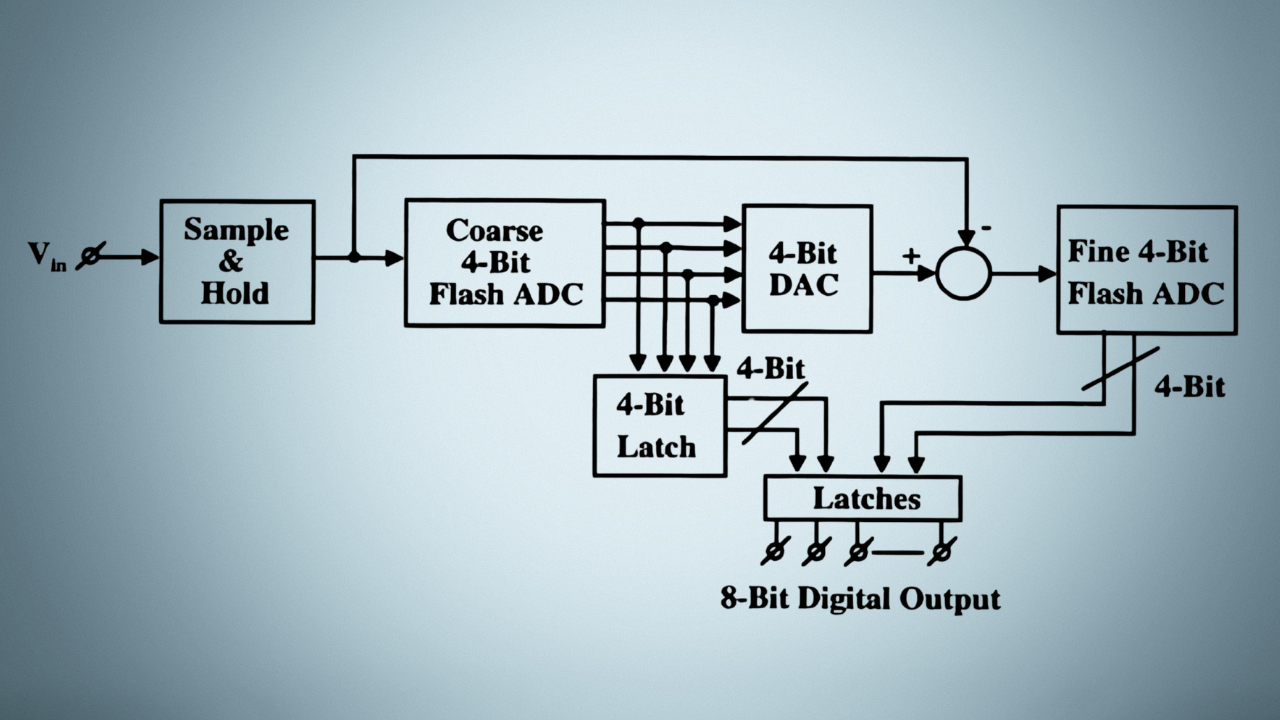

ADC Flash a Due Stadi

Questa architettura suddivide la conversione in due passaggi, utilizzando due convertitori Flash a bassa risoluzione in cascata:

- Il primo stadio converte i bit più significativi

- Un DAC ricostruisce il valore analogico corrispondente

- Un amplificatore di residuo calcola la differenza tra l’ingresso originale e il valore ricostruito

- Il secondo stadio converte i bit meno significativi dal segnale residuo

Questo approccio riduce drasticamente il numero di comparatori necessari. Ad esempio, un ADC a 8 bit può essere implementato con due stadi da 4 bit ciascuno, richiedendo solo 30 comparatori invece di 255.

Questo approccio riduce drasticamente il numero di comparatori necessari. Ad esempio, un ADC a 8 bit può essere implementato con due stadi da 4 bit ciascuno, richiedendo solo 30 comparatori invece di 255.

ADC Half-Flash

Questa architettura, nota anche come “Flash a 2 passi”, utilizza un singolo array di comparatori in due cicli successivi:

- Nel primo ciclo, il convertitore determina i bit più significativi

- In base al risultato, i riferimenti dei comparatori vengono riconfiguranti

- Nel secondo ciclo, vengono determinati i bit meno significativi

Questo approccio dimezza il numero di comparatori necessari a scapito di una riduzione della velocità.

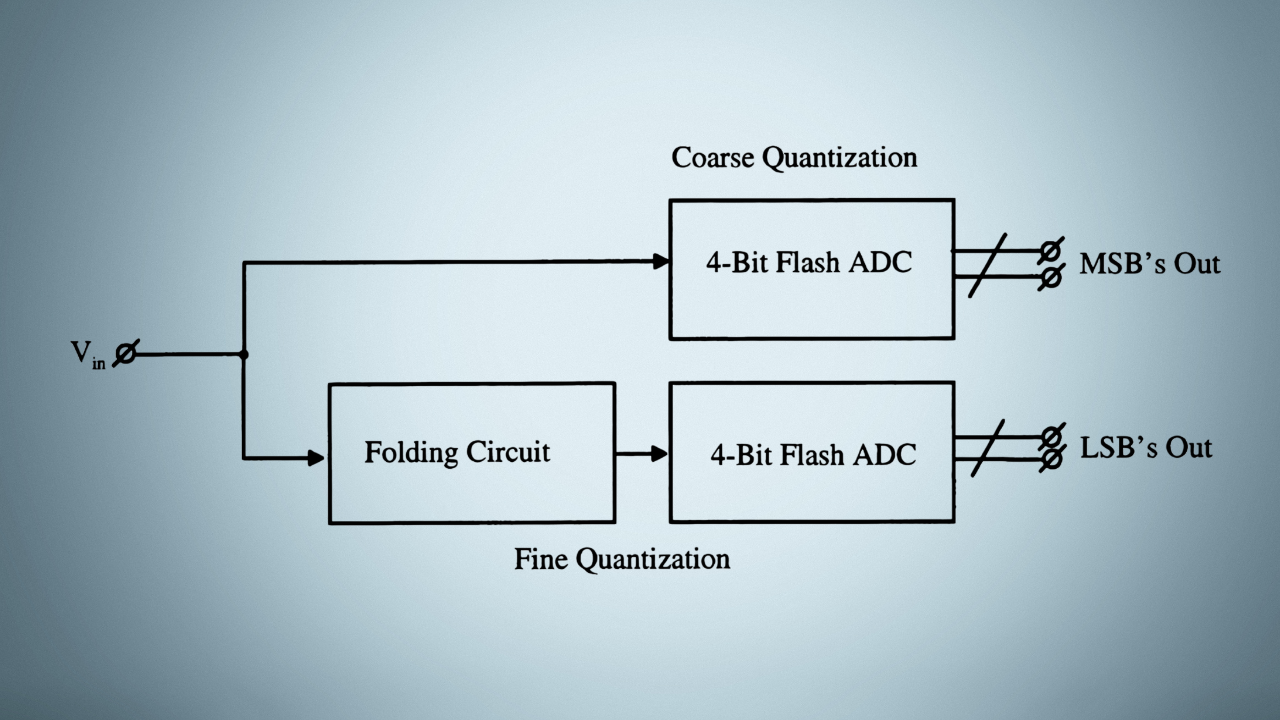

ADC Folding

L’architettura folding rappresenta un’evoluzione dell’approccio Flash che riduce significativamente la complessità hardware:

- Circuiti “folder” ripiegano il segnale di ingresso, riutilizzando gli stessi comparatori per diversi intervalli della scala

- Il numero di comparatori viene ridotto da esponenziale a lineare rispetto alla risoluzione

- Si mantiene gran parte del vantaggio di velocità dell’architettura Flash

Questa tecnica è particolarmente efficace per convertitori a media risoluzione (8-10 bit) e alta velocità.

Caso Applicativo: Ricevitore Software-Defined Radio con ADC Folding

Un esempio concreto di applicazione per un’architettura ibrida è rappresentato da un ricevitore Software-Defined Radio (SDR) per applicazioni militari o di telecomunicazione avanzata.

Scenario: Un sistema SDR militare deve coprire un’ampia gamma di frequenze (da pochi MHz a 6 GHz) con diverse modalità di modulazione, richiedendo un’elevata dinamica e buona risoluzione a velocità considerevoli.

Implementazione:

- Convertitore folding-interpolating a 10 bit con frequenza di campionamento di 250 MSPS

- Front-end RF con conversione diretta o a bassa IF per le bande di interesse

- FPGA ad alte prestazioni per l’elaborazione in tempo reale del flusso di dati

- Sistema di calibrazione dinamica per correggere le non-idealità del convertitore

Prestazioni:

- Banda analogica: >500 MHz

- ENOB: 8.7 bit a 100 MHz IF

- SFDR: >65 dB

- Consumo: 350 mW

Questa soluzione ibrida offre un eccellente compromesso tra velocità, risoluzione e consumo, permettendo di implementare un ricevitore flessibile in grado di adattarsi a diverse forme d’onda e condizioni operative, caratteristica essenziale per applicazioni SDR avanzate.

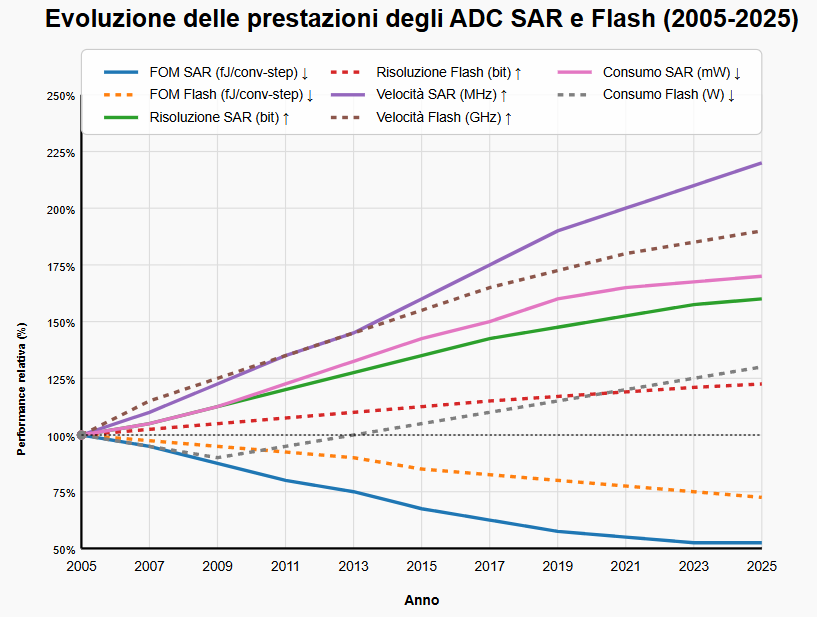

Evoluzione Tecnologica e Tendenze Future

Negli ultimi vent’anni, entrambe le architetture hanno beneficiato di significativi avanzamenti tecnologici:

Per i convertitori SAR:

- Implementazione di tecniche di campionamento asincrone per migliorare l’efficienza energetica

- Sviluppo di architetture time-domain che trasformano la tensione in timing per migliorare la scalabilità con processi nanometrici

- Tecniche di calibrazione background per compensare le non-idealità del DAC

- Architetture a risoluzione variabile che adattano dinamicamente precisione e consumo

Per i convertitori Flash:

- Comparatori a reazione rigenerativa con consumi drasticamente ridotti

- Nuove topologie di encoder digitale resistenti agli errori di bubble

- Tecniche di calibrazione digitale per compensare le variazioni di processo

- Integrazione di pre-amplificatori a basso rumore per migliorare la risoluzione effettiva

Tendenze Future

L’evoluzione delle tecnologie di processo e le emergenti necessità applicative stanno guidando alcune tendenze significative:

- Integrazione di Sistema: Crescente integrazione degli ADC in SoC complessi, con conseguente ottimizzazione dell’intera catena di acquisizione e elaborazione dati.

- Ottimizzazione per Tecnologie Nanometriche: Adattamento delle architetture per sfruttare i vantaggi dei processi nanometrici, privilegiando soluzioni basate più sul dominio temporale che su quello della tensione.

- Specializzazione Applicativa: Sviluppo di architetture ottimizzate per domini specifici come IoT, edge computing, automotive e 5G/6G.

- Tecniche di Machine Learning: Implementazione di algoritmi ML per calibrazione adattiva e compensazione degli errori, migliorando le prestazioni dinamiche.

Roadmap Tecnologica

Nei prossimi 3-5 anni, possiamo anticipare:

- ADC SAR con figure di merito sotto 1 fJ/conversione, abilitando nuove applicazioni ultra-low-power.

- Convertitori Flash con risoluzione estesa (10+ bit) mantenendo velocità di GSPS, grazie a tecniche avanzate di calibrazione.

- Maggiore integrazione di funzionalità di pre e post-elaborazione direttamente nei convertitori.

- Architetture riconfigurabile che possono adattarsi dinamicamente a diversi scenari operativi.

Considerazioni Economiche e di Mercato

Dopo aver evidenziato gli aspetti tecnici di questi dispositivi, è altrettanto importante dare uno sguardo ad altri parametri che influiscono grandemente sulla loro possibilità di utilizzo, ovvero i costi e la reperibilità delle diverse soluzioni:

ADC SAR:

- Range di prezzo: Da meno di $1 per versioni base a $20-50 per implementazioni ad alte prestazioni.

- Disponibilità: Ampia gamma di prodotti da numerosi fornitori.

- Costo di implementazione: Relativamente basso, con buona scalabilità.

ADC Flash:

- Range di prezzo: Da $5-10 per versioni semplici fino a $100-500 per soluzioni ad altissima velocità.

- Disponibilità: Limitate opzioni, specialmente per le versioni a più alta velocità.

- Costo di implementazione: Elevato, con significativi requisiti di potenza e raffreddamento.

Compromesso Costo-Prestazioni

La selezione del convertitore ottimale richiede una valutazione del TCO (Total Cost of Ownership):

- Costo diretto del componente: Generalmente più favorevole per soluzioni SAR a parità di risoluzione.

- Costo energetico: Significativamente inferiore per SAR, con impatto sul dimensionamento dell’alimentazione e sulla gestione termica.

- Costo di sviluppo: Potenzialmente maggiore per soluzioni Flash che richiedono particolare attenzione al routing, all’integrità del segnale e alla gestione EMI.

- Costo di opportunità: Da valutare in relazione alle prestazioni dell’intero sistema e ai vantaggi competitivi derivanti.

Caso pratico: In un sistema di acquisizione dati industriale, la scelta tra un ADC SAR a 16 bit/1 MSPS ($12) e un ADC Flash a 8 bit/500 MSPS ($35) deve considerare non solo le specifiche tecniche ma anche l’intero ciclo di vita del prodotto. Se l’applicazione richiede solo 500 kSPS con 14 bit di risoluzione, la soluzione SAR offre un significativo vantaggio economico non solo in termini di costo del componente, ma anche di sistema di alimentazione più semplice e minori requisiti di dissipazione termica.

Conclusione: Guida alla Selezione dell’Architettura Ottimale

La scelta tra convertitori SAR e Flash rappresenta un classico esempio di come l’ingegneria sia l’arte del compromesso. Non esiste una soluzione universalmente superiore, ma piuttosto un’architettura più adatta a ciascun contesto applicativo specifico.

Flowchart Decisionale

Il seguente processo decisionale può guidare la selezione iniziale:

- Determinare la frequenza di campionamento richiesta:

- Se > 100 MSPS, orientarsi verso architetture Flash o ibride

- Se < 20 MSPS, le architetture SAR offrono generalmente il miglior compromesso

- Valutare i requisiti di risoluzione:

- Se > 12 bit, le architetture SAR sono praticamente obbligatorie

- Se < 8 bit, considerare architetture Flash per vantaggi di velocità

- Analizzare i vincoli energetici:

- Con alimentazione a batteria o energy harvesting, privilegiare SAR

- Con alimentazione di rete e disponibilità di raffreddamento, Flash può essere accettabile

- Considerare i requisiti di latenza:

- Per sistemi di controllo in tempo reale, il ridotto ritardo delle architetture Flash può essere determinante

Considerazioni Finali

Nel panorama in continua evoluzione delle tecnologie di conversione, è fondamentale:

- Mantenersi aggiornati sulle più recenti innovazioni che possono alterare i tradizionali compromessi tra architetture.

- Valutare attentamente l’intero sistema, non solo le specifiche isolate del convertitore.

- Considerare implementazioni ibride che possono offrire il miglior compromesso per applicazioni specifiche.

- Verificare empiricamente le prestazioni in condizioni operative reali, non solo basandosi su specifiche teoriche.

Le architetture SAR e Flash continueranno a coesistere, evolvendosi per adattarsi a nuovi domini applicativi e tecnologie di processo. La comprensione approfondita dei loro punti di forza e delle loro limitazioni rimane uno strumento essenziale per ingegneri e manager di progetto nel campo dell’elettronica moderna.

Nel prossimo articolo della serie, esploreremo le architetture avanzate Sigma-Delta e Pipeline, che completano il quadro delle principali topologie di conversione analogico-digitale, offrendo ulteriori opzioni per applicazioni specifiche dove né SAR né Flash rappresentano la soluzione ottimale. A presto!