Analog To Digital – Fondamenti e principi della conversione

Lorenzo Martini, 09/04/2025

Il Processo di Conversione: Dalla Grandezza Fisica al Dato Digitale

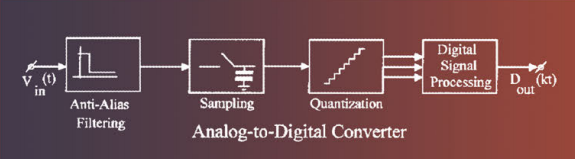

Il Flusso di Conversione

La trasformazione di un segnale analogico in formato digitale non è un processo immediato, ma una sequenza di operazioni che garantiscono l’integrità e l’accuratezza dell’informazione. Comprendere questi passaggi è fondamentale per apprezzare le complessità e i compromessi intrinseci alla conversione.

Il processo può essere schematizzato nelle seguenti fasi:

- Condizionamento del segnale: Il segnale analogico viene preparato per la conversione attraverso amplificazione, attenuazione, filtraggio e linearizzazione.

- Campionamento: Il segnale continuo viene rilevato a intervalli discreti di tempo, creando una sequenza di campioni.

- Mantenimento: Il valore campionato viene “congelato” per il tempo necessario alla conversione.

- Quantizzazione: Il valore analogico viene approssimato al livello discreto più vicino nella scala digitale disponibile.

- Codifica: Il valore quantizzato viene tradotto in una rappresentazione binaria.

Il Teorema del Campionamento di Nyquist-Shannon

Al cuore della teoria della conversione analogico-digitale risiede un principio matematico fondamentale: il Teorema del Campionamento di Nyquist-Shannon. Questo teorema stabilisce che, per ricostruire fedelmente un segnale analogico limitato in banda, la frequenza di campionamento deve essere almeno il doppio della massima frequenza presente nel segnale.

In termini formali:

fsample ≥ 2 * fmax

Dove:

- fsample è la frequenza di campionamento

- fmax è la massima frequenza presente nel segnale analogico

Questa relazione determina un vincolo fondamentale nella progettazione dei sistemi di conversione. Violare questo principio porta al fenomeno dell’aliasing, dove componenti ad alta frequenza vengono erroneamente rappresentate come frequenze più basse, introducendo distorsioni irreversibili nel segnale ricostruito.

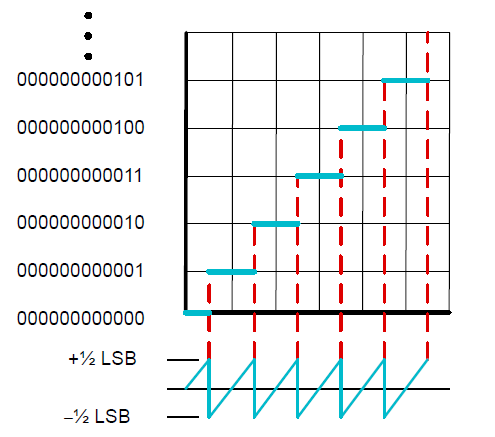

La Quantizzazione e l’Errore Intrinseco

La quantizzazione rappresenta una fonte intrinseca di errore nel processo di conversione. Quando un valore analogico continuo viene approssimato a uno dei livelli discreti disponibili, si introduce inevitabilmente un’incertezza, denominata errore di quantizzazione.

La massima ampiezza di questo errore è pari alla metà del passo di quantizzazione (LSB, Least Significant Bit), che corrisponde alla variazione minima rappresentabile dal convertitore. Statisticamente, assumendo una distribuzione uniforme del segnale di ingresso, l’errore di quantizzazione si manifesta come un rumore additivo con distribuzione uniforme nell’intervallo ±½ LSB.

Il rapporto segnale-rumore derivante da questo errore è direttamente proporzionale alla risoluzione del convertitore e può essere approssimato dalla formula:

SNR ≈ 6.02 · N + 1.76 dB

Dove N è il numero di bit del convertitore.

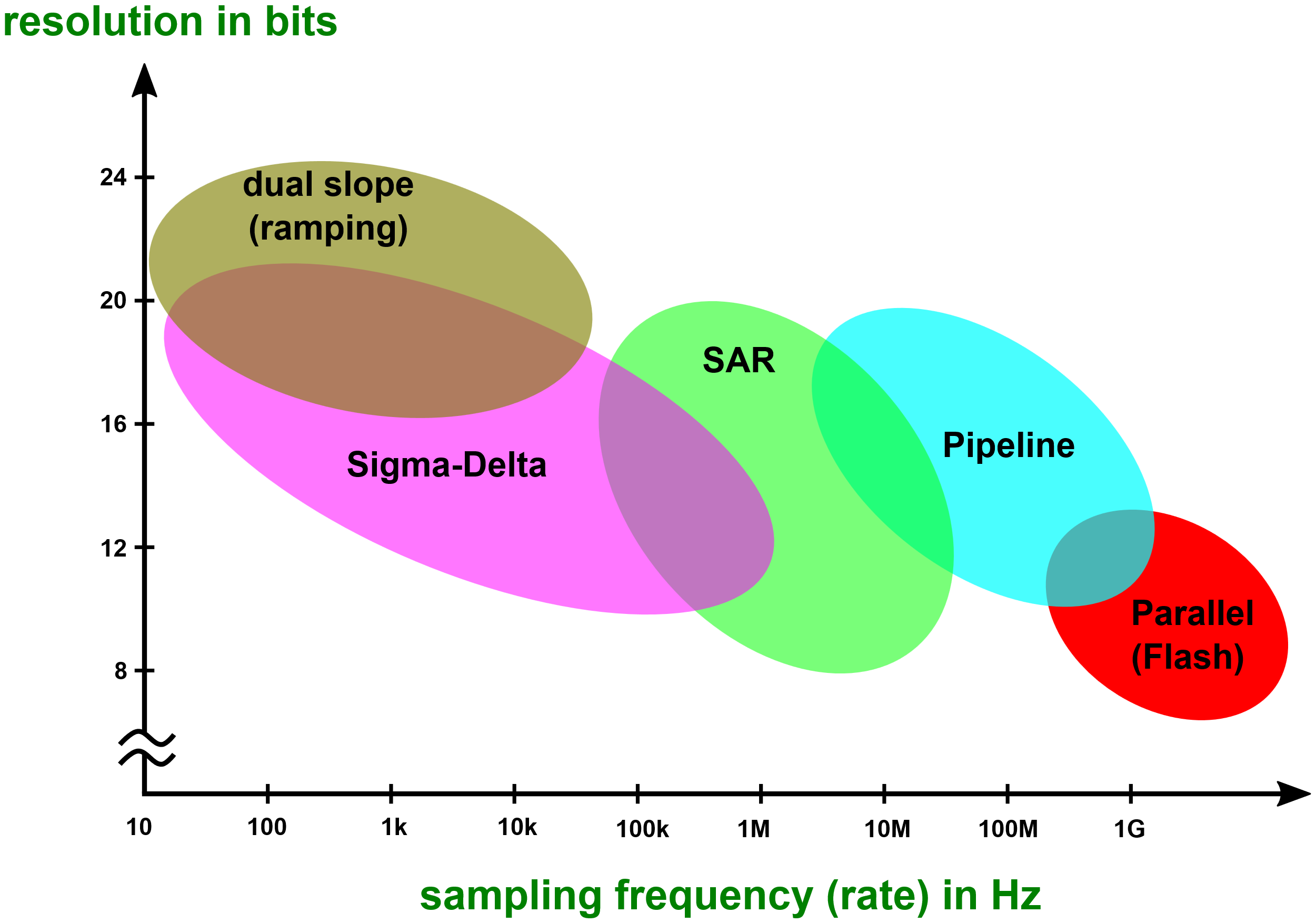

Architetture Principali dei Convertitori A/D

Le diverse applicazioni richiedono compromessi specifici tra velocità, precisione, consumo energetico e costo. Questo ha portato allo sviluppo di diverse architetture di ADC, ciascuna con caratteristiche distintive che la rendono ottimale per determinate applicazioni.

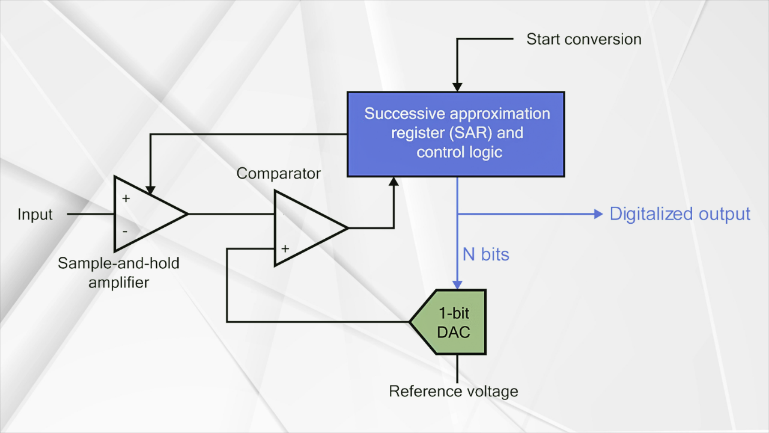

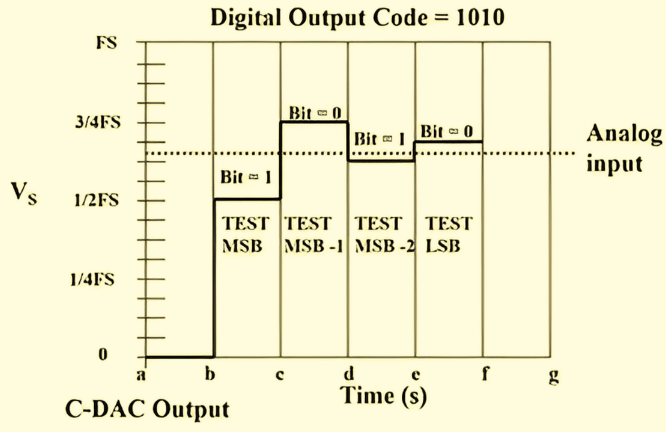

ADC ad Approssimazioni Successive (SAR)

L’architettura SAR implementa un algoritmo di ricerca binaria per determinare il valore digitale che meglio approssima l’ingresso analogico. Il processo inizia dal bit più significativo (MSB) e procede sequenzialmente verso il bit meno significativo (LSB).

Principio di funzionamento:

- Inizializzazione del registro SAR con il bit MSB a 1 e tutti gli altri a 0

- Conversione del valore digitale corrente in analogico tramite un DAC

- Confronto con il segnale di ingresso

- Se il valore DAC è maggiore dell’ingresso, il bit corrente viene azzerato

- Spostamento al bit successivo, impostandolo a 1

- Ripetizione dei passi 2-5 fino all’ultimo bit

Questa architettura offre un buon equilibrio tra velocità, precisione e consumo energetico, con tempi di conversione proporzionali alla risoluzione in bit.

Caso applicativo: Un sistema di acquisizione dati per analisi vibrazionale in ambito industriale richiede una risoluzione moderata (12-16 bit) con velocità di conversione di decine/centinaia di kilosample al secondo. L’ADC SAR rappresenta la soluzione ideale, offrendo un buon compromesso tra precisione e velocità, mantenendo consumi contenuti. Nella pratica, l’implementazione prevede un front-end analogico con filtri anti-aliasing configurati per limitare la banda del segnale a 40 kHz, seguito da un convertitore SAR a 16 bit con frequenza di campionamento di 100 kSPS. Questo approccio permette di analizzare con precisione fenomeni vibrazionali fino a 50 kHz, coprendo la maggior parte delle applicazioni di monitoraggio industriale.

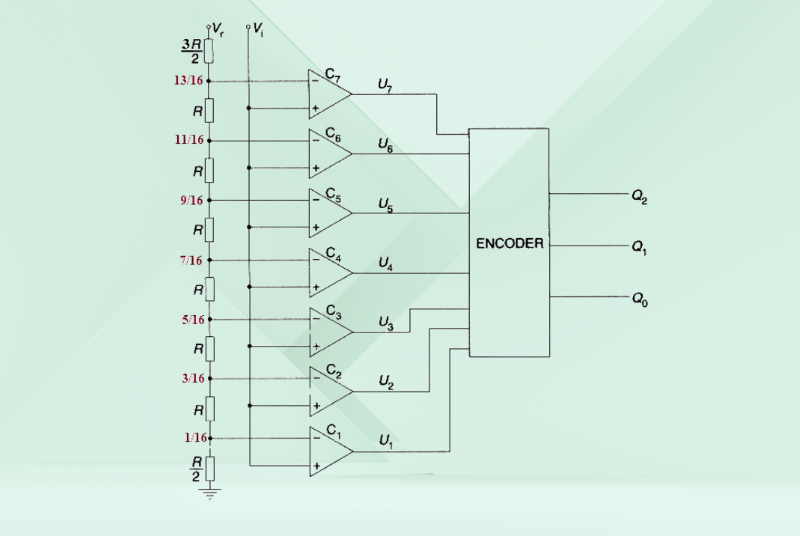

ADC Flash (Parallelo)

L’architettura Flash rappresenta l’approccio più diretto e veloce alla conversione, implementando simultaneamente tutti i comparatori necessari per determinare il codice digitale.

Principio di funzionamento:

- Una rete di resistori genera 2N-1 livelli di riferimento uniformemente distribuiti

- Ogni livello è collegato a un comparatore

- Il segnale di ingresso viene simultaneamente confrontato con tutti i livelli

- Un codificatore di priorità converte gli stati dei comparatori nel codice digitale finale

Questa architettura offre la massima velocità di conversione, ma con un costo esponenziale in termini di area, consumo e complessità all’aumentare della risoluzione.

Caso applicativo: Un ricevitore a radiofrequenza per telecomunicazioni richiede la digitalizzazione di segnali a banda larga con frequenze fino a centinaia di MHz. Un ADC Flash a 8 bit operante a 1 GSPS consente di campionare direttamente segnali IF (Intermediate Frequency) senza necessità di demodulazione analogica, semplificando l’architettura del ricevitore. Nella pratica, il segnale RF viene amplificato, filtrato e convertito a una frequenza intermedia di 200 MHz, quindi digitalizzato tramite un ADC Flash. Questa implementazione permette di realizzare in software funzioni come filtraggio, demodulazione e decodifica, aumentando la flessibilità del sistema e riducendo la complessità dell’hardware analogico.

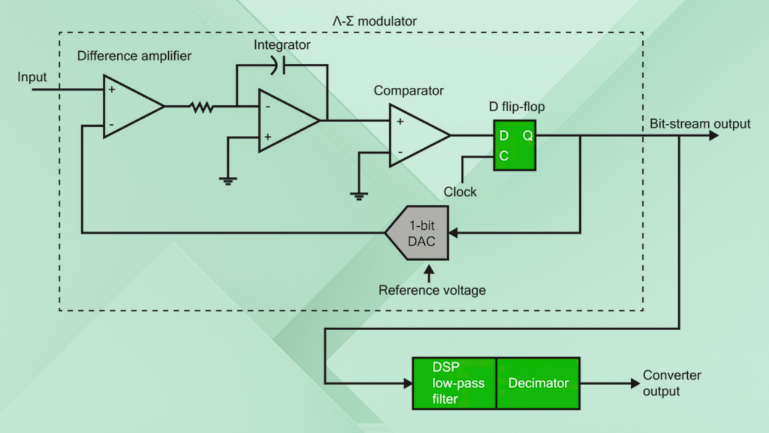

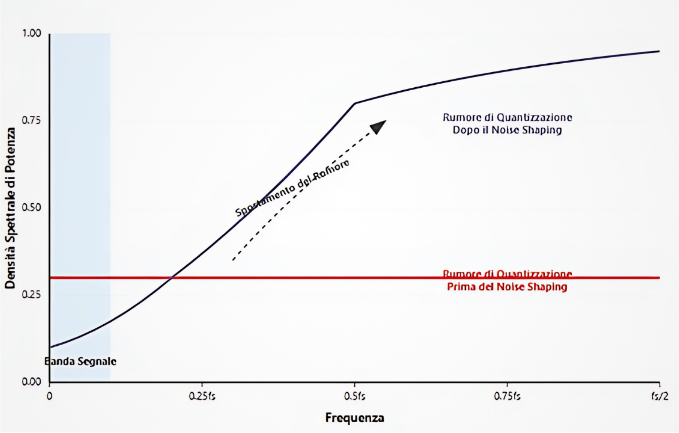

ADC Sigma-Delta (Σ-Δ)

L’architettura Sigma-Delta rappresenta un approccio radicalmente diverso, basato sul sovracampionamento e sulla modulazione del rumore di quantizzazione.

Principio di funzionamento:

- Il segnale viene campionato a una frequenza molto superiore a quella di Nyquist

- Un modulatore composto da un integratore e un quantizzatore a 1 bit genera una sequenza di bit

- Il rumore di quantizzazione viene modellato e spostato verso le alte frequenze

- Un filtro digitale decimatore rimuove il rumore ad alta frequenza e riduce la frequenza di campionamento

Questa architettura consente di ottenere risoluzioni estremamente elevate (fino a 24 bit e oltre) a scapito della banda passante.

Caso applicativo: Un sistema di acquisizione dati per misure di precisione in ambito scientifico necessita di risoluzioni estreme per rilevare variazioni minime di segnali a bassa frequenza. L’implementazione di un ADC Sigma-Delta a 24 bit con frequenza di campionamento effettiva di 10 SPS permette di raggiungere risoluzioni fino a 1 μV su scala di ±10V. Il sistema completo integra un front-end con amplificatore a guadagno programmabile e riferimenti di tensione ultra-stabili. Questa configurazione è ideale, ad esempio, per misure di resistività in materiali superconduttori, dove variazioni infinitesimali possono indicare transizioni di fase critiche.

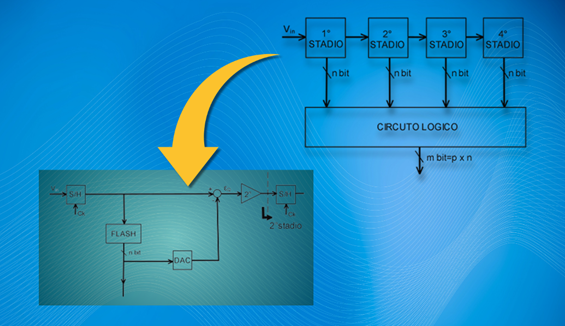

ADC Pipeline

L’architettura Pipeline rappresenta un compromesso tra la velocità dell’approccio Flash e l’efficienza dell’approccio SAR, implementando una sequenza di stadi di conversione parziale.

L’architettura Pipeline rappresenta un compromesso tra la velocità dell’approccio Flash e l’efficienza dell’approccio SAR, implementando una sequenza di stadi di conversione parziale.

Principio di funzionamento:

- Il segnale attraversa sequenzialmente più stadi di conversione

- Ogni stadio risolve alcuni bit (tipicamente da 1 a 4)

- Il residuo viene amplificato e passato allo stadio successivo

- I risultati parziali vengono ritardati opportunamente e combinati per formare il risultato finale

Questa architettura consente di ottenere alte velocità di campionamento mantenendo risoluzioni elevate (12-16 bit).

Caso applicativo: Un sistema di acquisizione video per applicazioni di imaging medicale richiede elevata risoluzione e alta velocità simultaneamente. Un ADC Pipeline a 14 bit con velocità di 80 MSPS consente di digitalizzare segnali video ad alta definizione preservando dettagli critici per la diagnosi. Nell’implementazione pratica, il segnale analogico proveniente dal sensore di immagine passa attraverso un circuito di sample-and-hold di precisione prima di entrare nel convertitore. La sincronizzazione precisa è garantita da un sistema di clock a basso jitter, essenziale per mantenere l’integrità dell’immagine. Questa soluzione permette di visualizzare in tempo reale immagini diagnostiche ad alta risoluzione, fondamentali in procedure come l’angiografia.

Parametri Fondamentali per la Valutazione degli ADC

La selezione del convertitore più adatto per una specifica applicazione richiede la comprensione e la valutazione di numerosi parametri che ne caratterizzano le prestazioni. Alcuni di questi sono di natura statica, altri dinamica, e la loro importanza relativa varia in base al contesto applicativo.

Parametri Statici

- Risoluzione: Numero di bit con cui viene rappresentato il segnale digitalizzato, determina il numero di livelli discreti disponibili (2N).

- Accuratezza assoluta: Massima deviazione tra il valore analogico reale e quello digitalizzato, considerando tutti gli errori.

- Errore di offset: Deviazione costante tra il valore ideale e quello reale, indipendente dall’ampiezza del segnale.

- Errore di guadagno: Variazione proporzionale all’ampiezza del segnale, rappresenta un errore di scala.

- Non linearità differenziale (DNL): Deviazione della larghezza effettiva di un passo di quantizzazione rispetto alla larghezza ideale.

- Non linearità integrale (INL): Deviazione della funzione di trasferimento rispetto alla retta ideale.

Parametri Dinamici

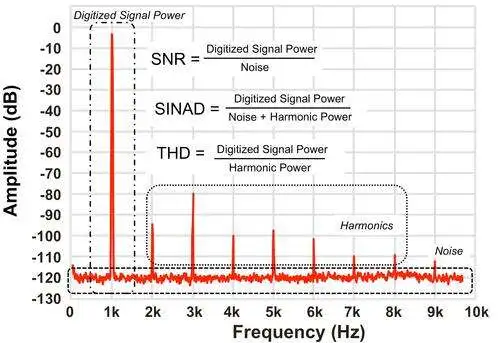

- Rapporto segnale-rumore (SNR): Rapporto tra la potenza del segnale e quella del rumore, espresso in dB.

- Distorsione armonica totale (THD): Misura delle componenti armoniche introdotte dal processo di conversione.

- Rapporto segnale-rumore e distorsione (SINAD): Combina SNR e THD in un unico parametro.

- Numero effettivo di bit (ENOB): Stima della risoluzione effettiva considerando gli effetti del rumore e della distorsione.

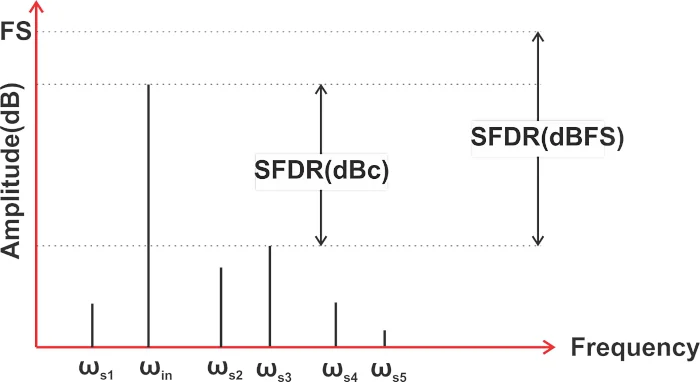

- Range dinamico privo di spurie (SFDR): Rapporto tra l’ampiezza del segnale fondamentale e quella della componente spuria più grande.

- Tempo di apertura (Aperture Delay): Ritardo tra il comando di campionamento e l’effettivo campionamento.

- Jitter di apertura: Variazione temporale casuale nel momento esatto di campionamento.

Parametri Funzionali e Operativi

- Frequenza di campionamento: Numero di campioni acquisiti per unità di tempo.

- Tempo di conversione: Intervallo necessario per completare una singola conversione.

- Tensione di riferimento: Valore che determina il fondo scala del convertitore.

- Impedenza di ingresso: Carico presentato al circuito che fornisce il segnale analogico.

- Consumo di potenza: Energia richiesta per il funzionamento, sia in modalità attiva che in standby.

- Interfaccia digitale: Protocollo di comunicazione utilizzato per trasferire i dati digitali (SPI, I²C, parallelo, ecc.).

Evoluzione Storica e Tendenze Tecnologiche

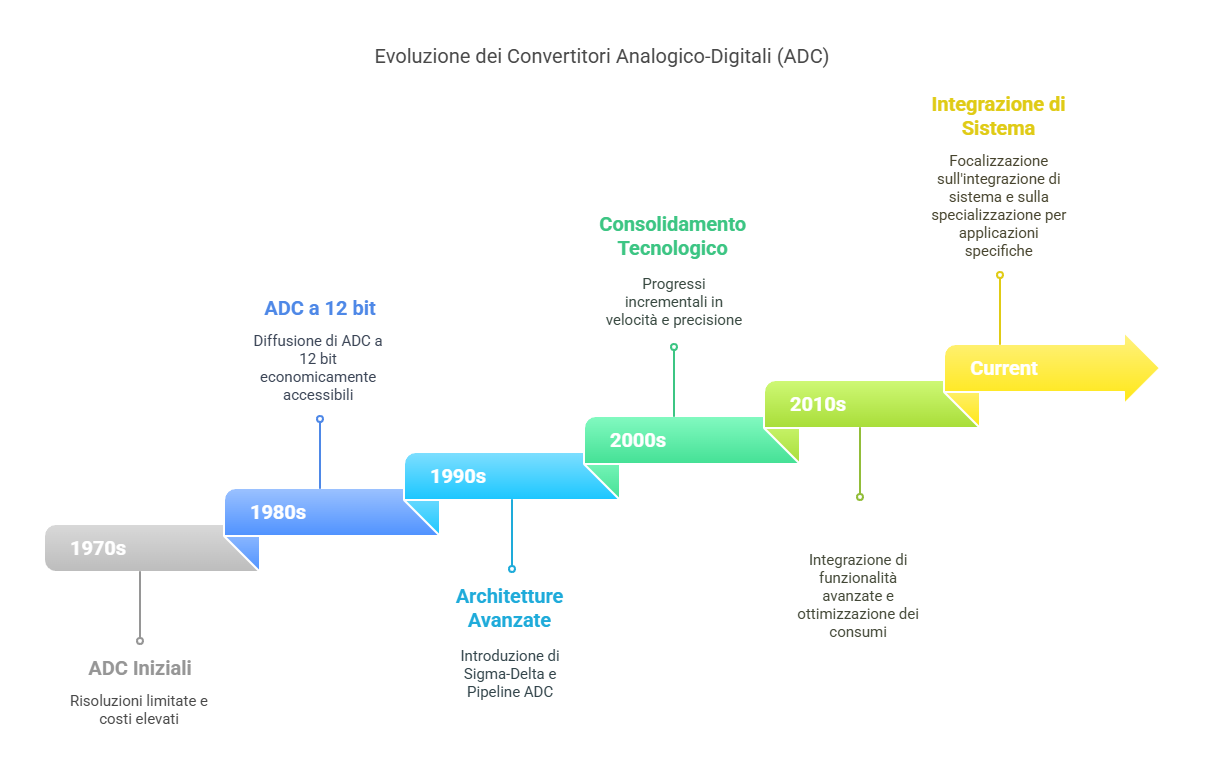

Dalle Origini all’Era Digitale

La conversione analogico-digitale ha radici che risalgono ai primi sistemi di telecomunicazione. Tuttavia, è solo con l’avvento dei semiconduttori integrati che i convertitori A/D hanno iniziato a diventare componenti diffusi e accessibili.

I primi ADC integrati degli anni ’70 offrivano risoluzioni limitate (8-10 bit) con velocità modeste e costi elevati. L’evoluzione tecnologica ha portato a progressivi miglioramenti in tutte le metriche prestazionali, seguendo una traiettoria simile alla legge di Moore per i processori:

- Anni ’80: Diffusione dei primi ADC a 12 bit economicamente accessibili

- Anni ’90: Introduzione di architetture avanzate come Sigma-Delta e Pipeline

- Anni 2000: Consolidamento della tecnologia con progressi incrementali in velocità e precisione

- Anni 2010: Integrazione di funzionalità avanzate e ottimizzazione dei consumi

- Attuale: Focalizzazione sull’integrazione di sistema e sulla specializzazione per applicazioni specifiche

Tendenze Tecnologiche Attuali

- Integrazione di Sistema: I moderni ADC raramente esistono come componenti isolati, ma sono integrati in sistemi più complessi che includono multiplexer analogici, amplificatori programmabili, riferimenti di tensione e interfacce digitali avanzate.

- Ottimizzazione Energetica: Con la proliferazione di dispositivi alimentati a batteria, l’efficienza energetica è diventata un parametro critico, portando allo sviluppo di architetture a bassissimo consumo e modalità di risparmio energetico avanzate.

- Specializzazione Applicativa: L’industria si sta muovendo verso soluzioni più specializzate, ottimizzate per domini applicativi specifici come biomedicale, automotive, comunicazioni o strumentazione.

- Integrazione con Elaborazione Digitale: L’emergere di architetture System-on-Chip ha portato a una maggiore integrazione tra la conversione e l’elaborazione digitale, con conseguente ottimizzazione dell’intero flusso di dati.

Conclusione: Il Ruolo Strategico degli ADC nell’Ecosistema Digitale

I convertitori analogico-digitali rappresentano uno degli elementi più critici nell’interfaccia tra il mondo fisico e quello digitale. La loro qualità determina il limite superiore delle prestazioni che un sistema può raggiungere, stabilendo un “collo di bottiglia” fondamentale nel flusso informativo.

La comprensione approfondita dei principi operativi, delle architetture disponibili e dei parametri prestazionali consente di effettuare scelte consapevoli nella selezione e nell’implementazione di questi componenti critici.

Nei prossimi articoli di questa serie, approfondiremo ciascuna delle principali architetture, analizzeremo le tecniche di caratterizzazione e testing, esploreremo le considerazioni pratiche di implementazione e discuteremo i casi applicativi più significativi in vari settori industriali.

Punti Chiave da Ricordare

- La conversione analogico-digitale è un processo multi-fase che include campionamento, quantizzazione e codifica

- Il teorema di Nyquist-Shannon stabilisce i vincoli fondamentali per un campionamento fedele

- Diverse architetture (SAR, Flash, Sigma-Delta, Pipeline) offrono compromessi specifici tra velocità, precisione e consumo

- La valutazione completa di un ADC richiede la considerazione di parametri sia statici che dinamici

- L’evoluzione tecnologica continua a spingere verso maggiore integrazione, efficienza energetica e specializzazione applicativa

Approfondimenti Suggeriti

Per approfondire ulteriormente i concetti trattati in questo articolo, suggeriamo:

- Lettura del prossimo articolo della serie, focalizzato sulle architetture SAR e Flash

- Esplorazione delle specifiche tecniche di convertitori commerciali per comprendere l’interpretazione pratica dei parametri

- Familiarizzazione con gli strumenti di simulazione per la modellazione del comportamento dei convertitori

- Studio delle tecniche di condizionamento del segnale, essenziali per sfruttare pienamente le potenzialità degli ADC