Disposizione dei layers in un PCB – Una guida Pratica (Parte 1 – Fondamenti tecnici)

Lorenzo Martini, 03/04/2025

Nell’era dell’elettronica miniaturizzata e delle crescenti frequenze operative, la disposizione dei layer nei circuiti stampati (PCB) rappresenta una decisione progettuale fondamentale che influenza direttamente prestazioni, affidabilità e costi. Mentre i primi circuiti stampati erano semplici strutture single-layer, l’evoluzione tecnologica ha portato alla diffusione di PCB multi-layer sempre più complessi, in grado di supportare densità di componenti e frequenze operative impensabili solo pochi decenni fa.

La progettazione dello stackup (disposizione dei layer) è diventata una disciplina sofisticata che bilancia considerazioni elettriche, termiche, meccaniche ed economiche. Una configurazione ottimale può migliorare significativamente l’integrità del segnale, ridurre le emissioni elettromagnetiche e semplificare il processo produttivo, mentre scelte inadeguate possono causare malfunzionamenti, superamento dei limiti EMC e costi di produzione eccessivi.

Il passaggio da circuiti single-layer a strutture multi-layer non rappresenta semplicemente un’evoluzione tecnica incrementale, ma un vero e proprio cambio di paradigma nella progettazione elettronica. Con l’introduzione di ogni layer aggiuntivo, la complessità aumenta esponenzialmente, creando nuove opportunità ma anche nuove sfide. In questo contesto, la comprensione approfondita delle dinamiche di interazione tra i diversi strati diventa fondamentale per ogni progettista.

Quali sono quindi i principi fondamentali che guidano la progettazione di stackup efficaci? Come si possono ottimizzare le configurazioni per specifiche applicazioni? Questo articolo esplora le strategie fondamentali per una corretta disposizione dei layer nei PCB moderni, offrendo linee guida pratiche per progettisti di diversi livelli e decision-maker tecnici che necessitano di comprendere le implicazioni di queste scelte architetturali.

Fondamenti dello stackup nei PCB

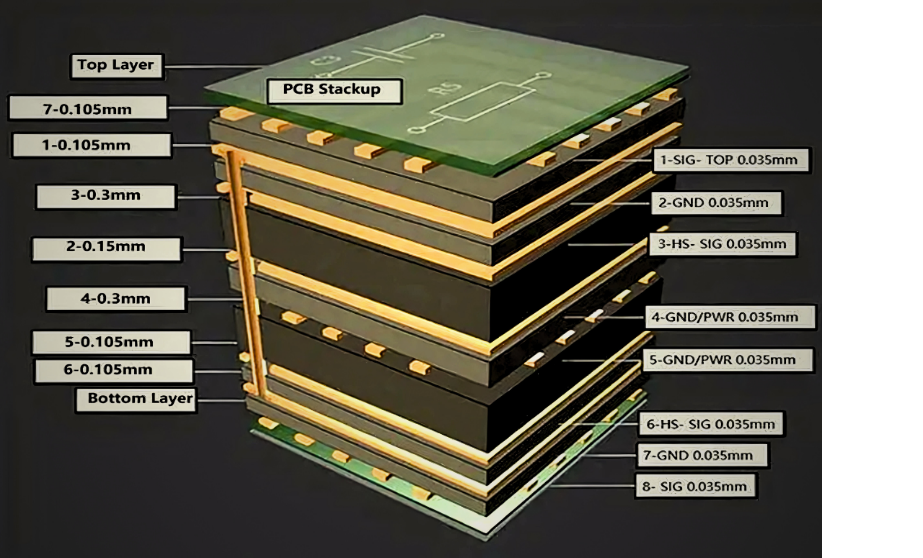

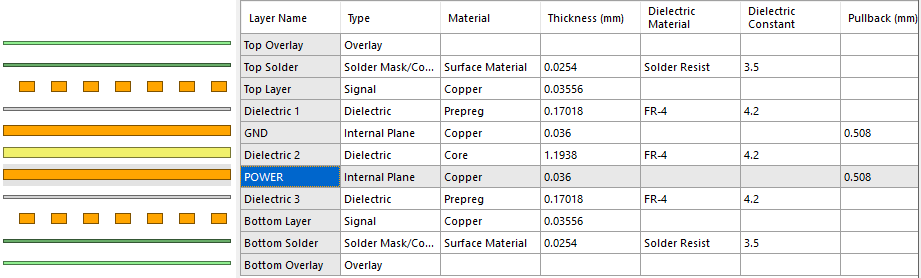

Un PCB multi-layer è composto essenzialmente da strati conduttivi (tipicamente rame) alternati a materiali isolanti (substrati). La configurazione di questi strati, nota come “stackup”, determina molte caratteristiche elettriche, termiche e meccaniche del circuito finale.

I materiali isolanti, spesso denominati “prepreg” e “core”, differiscono principalmente nel loro stato di lavorazione: il core è già completamente polimerizzato, mentre il prepreg si solidifica durante il processo di laminazione. Questa distinzione ha conseguenze rilevanti per la stabilità dimensionale e le caratteristiche elettriche del PCB finale.

I layer in un PCB possono essere classificati in quattro tipologie principali:

- Layer di segnale: Dedicati alla trasmissione dei segnali tra i componenti

- Piani di alimentazione: Forniscono distribuzione dell’energia (12V, 3.3V, ecc.)

- Piani di massa: Offrono un riferimento comune e percorsi di ritorno per i segnali

- Layer misti: Combinano segnali e porzioni di piano (tipici in PCB con meno layer)

La simmetria nella disposizione dei layer è un principio fondamentale per prevenire deformazioni del PCB durante i processi termici di produzione. Uno stackup simmetrico distribuisce uniformemente lo stress termico, riducendo significativamente il rischio di warping (curvatura) e twisting (torsione). Questa simmetria riguarda non solo il numero di layer, ma anche la disposizione del rame, che dovrebbe essere bilanciata rispetto al piano centrale del PCB.

La continuità dei piani di riferimento contribuisce in modo determinante all’efficacia dello stackup. Un piano frammentato può compromettere l’integrità del segnale, creando percorsi di ritorno della corrente imprevedibili. Nei PCB ad alta frequenza, i percorsi di ritorno tendono a seguire il principio del “percorso a minima induttanza”, posizionandosi direttamente sotto la traccia di andata. L’interruzione del piano di riferimento costringe la corrente a deviazioni che aumentano l’area del loop, incrementando emissioni e suscettibilità alle interferenze.

Un aspetto spesso trascurato è la “spaziatura critica” tra i layer, che influenza diversi parametri elettrici. L’ottimizzazione di questa distanza, particolarmente tra layer di segnale e relativi piani di riferimento, contribuisce significativamente alle prestazioni complessive del PCB, specialmente per quanto riguarda l’immunità al rumore e l’integrità del segnale.

Configurazioni comuni per diversi numeri di layer

PCB a 2 layer

La configurazione più semplice dopo il single-layer, comprende:

Layer 1 (Top): tipicamente componenti e segnali

Layer 2 (Bottom): principalmente segnali e talvolta componenti

Un unico substrato tra i due layer

Questa configurazione è economica e adatta per circuiti semplici a bassa frequenza, ma presenta limitazioni significative per l’integrità del segnale e la gestione EMI.

L’assenza di un piano di riferimento dedicato nei PCB a 2 layer impone considerazioni particolari durante il routing. Una pratica efficace consiste nel creare aree di massa il più ampie possibile, specialmente sotto componenti critici come oscillatori o regolatori di tensione. Nei circuiti digitali a bassa velocità, è comune utilizzare una griglia di tracce di massa che forma una sorta di “pseudo-piano”, migliorando le prestazioni EMI senza richiedere layer aggiuntivi.

Nei PCB a 2 layer, la strategia di routing assume un’importanza fondamentale. Un approccio efficace consiste nel disporre i segnali critici sul top layer, mantenendo il bottom layer per segnali meno sensibili e per una distribuzione di massa il più continua possibile. L’orientamento ortogonale delle tracce tra i due layer (orizzontale sul top, verticale sul bottom o viceversa) riduce le interferenze tra segnali che si incrociano.

Caso applicativo: Termostato domestico intelligente

Un termostato smart rappresenta un esempio ideale di applicazione a 2 layer. Il circuito comprende tipicamente un microcontrollore a bassa potenza, sensori ambientali e un’interfaccia utente, operanti a frequenze relativamente basse (sotto i 20 MHz).

Nella progettazione di questo dispositivo, il top layer ospita il microcontrollore e i componenti principali, con un’area di massa dedicata sotto l’oscillatore. I segnali analogici dei sensori di temperatura vengono instradati sul top layer con percorsi brevi e diretti, mentre il bottom layer contiene prevalentemente una distribuzione di massa e le connessioni all’interfaccia utente.

Per migliorare l’integrità del segnale, il progettista ha implementato le seguenti strategie:

- Separazione dei circuiti analogici e digitali con zone di massa distinte

- Routing a “T” per minimizzare stub nelle connessioni critiche

- Utilizzazione di componenti di disaccoppiamento strategicamente posizionati

- Piano di massa parziale sotto i sensori analogici per ridurre il rumore

Questo approccio ha permesso di ottenere prestazioni affidabili mantenendo i costi di produzione contenuti, aspetto essenziale per un prodotto destinato al mercato consumer.

PCB Multistrato

La minimizzazione dello spazio tra il percorso del segnale e quello della sua corrente di ritorno verso la sorgente, costituisce un obiettivo imprescindibile per ridurre le EMI e diventa essenziale con l’aumentare delle frequenze del segnale: è evidente che rispettare questa regola risulta praticamente impossibile in un circuito a 2 strati. Un rimedio consiste nell’aggiungere piani di massa molto vicini ai piani di segnale, che permettano alle correnti di trovare il loro percorso di ritorno ottimale, minimizzando l’area della spira formata dai percorsi di andata e ritorno della corrente associata ad un dato segnale. L’aggiunta di piani permette anche una distribuzione ottimale delle alimentazioni, fornendo alle correnti percorsi ad impedenza minima e creando, insieme ai piani di massa, una stabilizzazione capacitiva in grado di agire come un filtro passa basso.

PCB a 4 layer

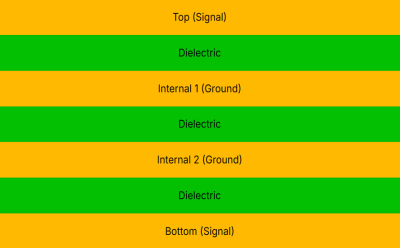

Una configurazione molto diffusa per applicazioni di media complessità può essere la seguente:

Layer 1 (Top): Segnale

Layer 1 (Top): Segnale

Layer 2 (Inner Plane): GND

Layer 3 (Inner Plane): Alimentazione

Layer 4 (Bottom): Segnale

Questo stackup offre:

- Distribuzione uniforme dell’alimentazione

- Buon riferimento di massa per i segnali

- Accoppiamento capacitivo tra piani di alimentazione e massa

- Percorsi di ritorno della corrente ben definiti

Il posizionamento dei piani all’interno dello stackup offre un ulteriore vantaggio: la schermatura intrinseca. I piani interni, specialmente quello di massa, agiscono come barriere elettromagnetiche, riducendo l’accoppiamento tra i layer di segnale esterni e migliorando la compatibilità elettromagnetica complessiva del dispositivo.

Un aspetto cruciale nei PCB a 4 layer è la gestione delle transizioni tra layer (vias). Ogni via rappresenta una discontinuità nell’impedenza che può compromettere l’integrità del segnale alle alte frequenze. Un attento posizionamento dei vias, specialmente per segnali critici, contribuisce significativamente alle prestazioni complessive del circuito.

Nella configurazione degli strati riportata sopra, la vicinanza del layer di segnale Top a un piano di massa ottimizza i percorsi di ritorno delle correnti e crea un sistema di trasmissione controllato, riducendo drasticamente emissioni e diafonia. Questa ottimizzazione, però, non si replica nello strato di segnale Bottom. Per applicazioni più sensibili alle interferenze, una variante ottimizzata potrebbe essere:

Layer 1 (Top): Segnale

Layer 2 (Inner Plane): GND

Layer 3 (Inner Plane): GND

Layer 4 (Bottom): Segnale

con i piani di alimentazione realizzati parzialmente sui layer 1 e 4. Questa configurazione, conosciuta come “power islands”, migliora ulteriormente l’integrità del segnale a scapito di una distribuzione dell’alimentazione meno efficiente.

Sono ovviamente possibili anche altre configuazioni, tra le quali vale la pena segnalare l’inversione tra il Bottom layer e il piano interno di massa adiacente (layer 3), in modo da “seppellire” le tracce di segnale e schermarle ulteriormente (striplines), aumentando le frequenze gestibili.

Caso applicativo: Sistema di acquisizione dati industriale

Un sistema di acquisizione dati per ambiente industriale rappresenta un’applicazione ideale per un PCB a 4 layer. Il dispositivo include convertitori analogico-digitali di precisione, un processore di segnale digitale (DSP) e interfacce di comunicazione operanti a frequenze intermedie (50-100 MHz).

In questo progetto, lo stackup è stato ottimizzato come segue:

Layer 1 (Top): Componenti e segnali analogici, con aree dedicate per segnali digitali veloci

Layer 2 (GND): Piano di massa continuo senza interruzioni

Layer 3 (Power): Multipli piani di alimentazione segmentati (3.3V digitale, 5V analogico, ecc.)

Layer 4 (Bottom): Principalmente segnali digitali e interconnessioni meno critiche

Per garantire l’integrità del segnale, il progettista ha implementato strategie avanzate:

- Routing differenziale per interfacce seriali veloci

- Separazione fisica tra sezioni analogiche e digitali

- Via stitching per collegare efficacemente i piani di massa tra layer 1 e 2

- Piano di alimentazione segmentato sul layer 3 per isolare diversi domini di potenza

Questa configurazione ha permesso di ottenere un’eccellente reiezione al rumore ambiente, essenziale in contesti industriali, mantenendo costi di produzione ragionevoli per un dispositivo di fascia media.

PCB a 6 layer

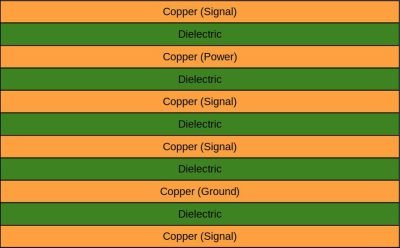

La sempre maggiore aggressività sui prezzi, soprattutto da parte dei fabbricanti di PCB orientali, ha portato lo stackup a 6 layer a rappresentare un buon compromesso tra costo e prestazioni per applicazioni più complesse. La miniaturizzazione dei circuiti e il vertiginoso aumento dei pin per accedere ai segnali dei chips richiede, infatti, un ulteriore aumento degli strati del PCB per uno sbroglio corretto delle piste di collegamento. Una possibile configurazione che privilegi il numero di strati di segnale può essere la seguente:

Layer 1 (Top): Segnale

Layer 1 (Top): Segnale

Layer 2 (Inner Plane): Alimentazione

Layer 3 (Inner Plane): Segnale

Layer 4 (Inner Plane): Segnale

Layer 5 (Inner Plane): GND

Layer 6 (Bottom): Segnale

Una tale configurazione però non si coniuga, per quanto già visto in merito all’ottimizzazione dei percorsi di ritorno delle correnti, con la gestione di segnali ad alta frequenza e di possibili problematiche di cross-talking ed EMI in generale. Per prestazioni EMC migliori e cercando di mantenere una distribuzione ottimizzata dell’alimentazione, può essere adottata la seguente configurazione:

Layer 1 (Top): Segnale

Layer 1 (Top): Segnale

Layer 2 (Inner Plane): GND

Layer 3 (Inner Plane): Alimentazione

Layer 4 (Inner Plane): Segnale

Layer 5 (Inner Plane): GND

Layer 6 (Bottom): Segnale

L’aggiunta di due layer rispetto alla configurazione a 4 layer introduce una flessibilità significativa nella gestione dei segnali. I layer interni possono essere dedicati a segnali specifici, come bus di dati o clock ad alta velocità, beneficiando della schermatura offerta dai piani adiacenti.

In uno stackup a 6 layer, la gestione dell’impedenza diventa più sofisticata. I layer interni permettono la realizzazione di stripline (linee di trasmissione completamente racchiuse tra piani di riferimento), che offrono una migliore immunità alle interferenze rispetto alle microstrip presenti sui layer esterni. Questo favorisce una progettazione più robusta per segnali ad alta velocità.

La scelta tra le due configurazioni presentate dipende principalmente dalle esigenze specifiche del progetto. Come detto, la prima configurazione massimizza la superficie disponibile per il routing, mentre la seconda ottimizza la schermatura e la distribuzione dell’alimentazione. Quest’ultima è preferibile per applicazioni con stringenti requisiti EMC o frequenze operative elevate.

Un aspetto importante nella progettazione a 6 layer è la gestione termica. Con l’aumento della densità di componenti e della dissipazione di potenza, i piani di massa e alimentazione possono svolgere un ruolo cruciale nella distribuzione del calore. Un’attenta progettazione termica, che includa via termici strategicamente posizionati, contribuisce alla longevità e all’affidabilità del dispositivo.

Caso applicativo: Gateway IoT industriale

Un gateway IoT industriale rappresenta un’applicazione emblematica per un PCB a 6 layer. Il dispositivo integra un processore performante, memorie ad alta velocità, multiple interfacce di comunicazione (Ethernet, Wi-Fi, cellulare) e circuiti di alimentazione complessi.

Un gateway IoT industriale rappresenta un’applicazione emblematica per un PCB a 6 layer. Il dispositivo integra un processore performante, memorie ad alta velocità, multiple interfacce di comunicazione (Ethernet, Wi-Fi, cellulare) e circuiti di alimentazione complessi.

In questo progetto, lo stackup è stato configurato come segue:

- Layer 1 (Top): Componenti principali e segnali ad alta frequenza (Wi-Fi, RF)

- Layer 2 (GND): Piano di massa continuo

- Layer 3 (Segnale): Bus di memoria e segnali digitali veloci

- Layer 4 (Alimentazione): Distribuzione di multiple tensioni con segmentazione

- Layer 5 (GND): Secondo piano di massa

- Layer 6 (Bottom): Componenti secondari e segnali meno critici

La progettazione ha incorporato tecniche avanzate:

- Controllo dell’impedenza per tutti i segnali differenziali (USB, Ethernet)

- Routing a “picket fence” per minimizzare la diafonia tra segnali paralleli

- Isolamento RF con strutture a “fence via” intorno ai circuiti wireless

- Zone di alimentazione dedicate con filtraggio localizzato

L’adozione di un PCB a 6 layer ha permesso di gestire efficacemente l’elevata complessità del sistema, garantendo contemporaneamente eccellenti prestazioni EMC e affidabilità in ambienti industriali impegnativi.

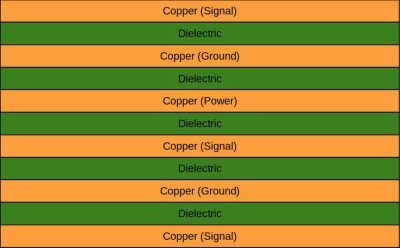

PCB a 8+ layer

Per applicazioni ad alta complessità e frequenza, gli stackup da 8, 10, 12 o più layer offrono:

- Separazione dei segnali critici

- Multiple alimentazioni

- Migliore schermatura

- Maggiore flessibilità nel routing

Un esempio di stackup a 8 layer potrebbe essere:

- Layer 1 (Top): Segnale

- Layer 2 (Inner layer): GND

- Layer 3 (Inner layer): Segnale

- Layer 4 (Inner layer): Alimentazione

- Layer 5 (Inner layer): GND

- Layer 6 (Inner layer): Segnale

- Layer 7 (Inner layer): GND

- Layer 8 (Bottom): Segnale

Con l’aumento del numero di layer, la complessità della progettazione cresce significativamente, ma aumentano anche le potenzialità. La presenza di multipli piani di massa e alimentazione permette una segmentazione sofisticata dei domini di potenza, essenziale per sistemi che incorporano circuiti analogici, digitali e RF in stretta prossimità.

Negli stackup avanzati, il concetto di “segregazione verticale” diventa fondamentale. I segnali possono essere organizzati non solo per dominio funzionale (analogico, digitale, potenza), ma anche per livello di criticità o banda di frequenza. Ad esempio, i segnali ad alta velocità possono essere confinati in layer specifici, ottimizzati per queste applicazioni.

La ridondanza dei piani di riferimento migliora drammaticamente la robustezza elettromagnetica del sistema. In applicazioni con stringenti requisiti di immunità o basse emissioni, questa caratteristica può essere determinante per il successo del progetto, eliminando la necessità di costose schermature esterne o filtri aggiuntivi, da tenere in conto nel budget del prodotto.

Un elemento distintivo degli stackup avanzati è la possibilità di implementare strutture guidate particolari, come stripline asimmetriche o broadside coupled, che offrono caratteristiche elettriche superiori per applicazioni critiche. Queste configurazioni richiedono un’attenta progettazione e collaborazione con il produttore di PCB, ma possono offrire vantaggi significativi in termini di prestazioni.

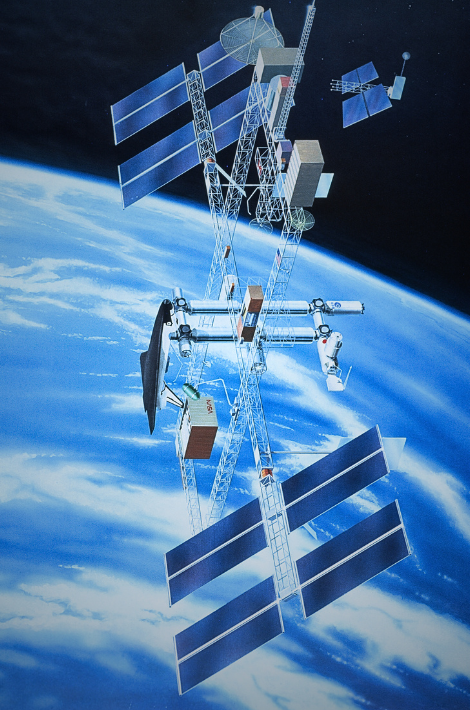

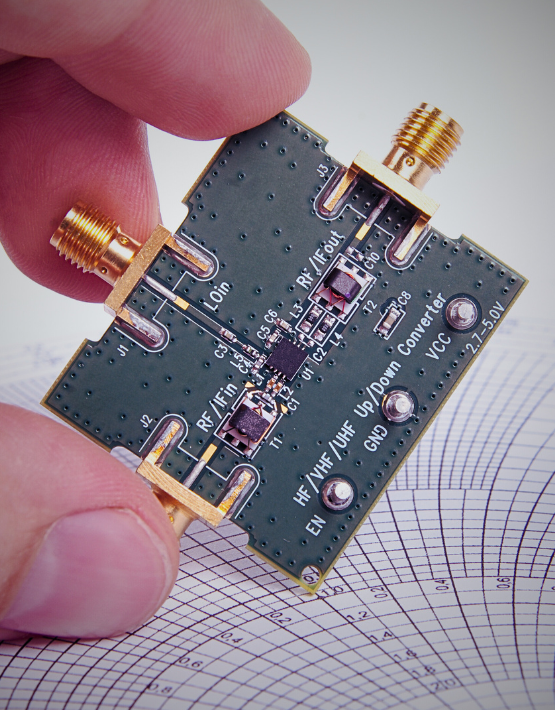

Caso applicativo: Sistema di comunicazione satellitare

Un terminale di comunicazione satellitare rappresenta un esempio paradigmatico di applicazione che richiede un PCB a 10 layer. Il sistema integra sezioni RF ad alta frequenza (fino a 12 GHz), elaborazione digitale del segnale complessa e gestione dell’alimentazione sofisticata.

In questo progetto avanzato, lo stackup è stato progettato come segue:

In questo progetto avanzato, lo stackup è stato progettato come segue:

- Layer 1 (Top): Componenti RF e circuiti a microonde

- Layer 2 (GND): Piano di massa dedicato RF

- Layer 3 (Segnale): Linee di trasmissione RF controllate

- Layer 4 (GND): Piano di massa di isolamento

- Layer 5 (Alimentazione): Distribuzione alimentazioni analogiche

- Layer 6 (GND): Piano di massa centrale

- Layer 7 (Segnale): Bus di dati ad alta velocità

- Layer 8 (Alimentazione): Distribuzione alimentazioni digitali

- Layer 9 (GND): Piano di massa digitale

- Layer 10 (Bottom): Circuiti digitali e componenti di supporto

Questa configurazione implementa una segregazione completa tra circuiti RF, analogici e digitali, con piani di massa dedicati per ciascun dominio. Le strategie avanzate includono:

- Transizioni ottimizzate tra microstrip e stripline per segnali a microonde

- Strutture risonanti embedded nei layer interni per filtraggio RF

- Distribuzione termica attraverso una rete pianificata di via termici

- Schermatura a compartimenti tra sezioni sensibili

L’adozione di un PCB così sofisticato ha permesso di integrare in un singolo dispositivo funzionalità che tradizionalmente avrebbero richiesto multiple schede separate, riducendo dimensioni, peso e consumi energetici – aspetti critici per applicazioni spaziali.

Principi avanzati di disposizione dei layer

Accoppiamento dei piani

La distanza tra piani di alimentazione e massa influisce significativamente sulla capacità di bypass distribuita, che filtra naturalmente il rumore. Un minor spessore del dielettrico tra questi piani aumenta la capacità di disaccoppiamento e migliora le prestazioni alle alte frequenze.

L’effetto capacitivo tra piani adiacenti non è un fenomeno secondario, ma una caratteristica progettuale fondamentale che può essere sfruttata strategicamente. La capacità distribuita tra piani di alimentazione e massa crea un sistema di filtraggio naturale che può essere quantificato e ottimizzato. Per un sistema digitale tipico, questa capacità si aggira intorno a 75-100 pF per pollice quadrato, valore che può essere significativamente aumentato riducendo lo spessore del dielettrico o utilizzando materiali ad alta costante dielettrica.

L’effetto capacitivo tra piani adiacenti non è un fenomeno secondario, ma una caratteristica progettuale fondamentale che può essere sfruttata strategicamente. La capacità distribuita tra piani di alimentazione e massa crea un sistema di filtraggio naturale che può essere quantificato e ottimizzato. Per un sistema digitale tipico, questa capacità si aggira intorno a 75-100 pF per pollice quadrato, valore che può essere significativamente aumentato riducendo lo spessore del dielettrico o utilizzando materiali ad alta costante dielettrica.

Oltre alla distanza, la continuità dei piani e la loro integrità strutturale influenzano direttamente l’efficacia di questo accoppiamento. Le fessure nei piani, necessarie per via o per isolamento, creano discontinuità che possono compromettere le prestazioni alle alte frequenze. Tecniche come “via stitching” e “moat” permettono di mantenere l’integrità dei piani pur rispettando vincoli di isolamento elettrico.

In sistemi ad alta velocità, l’accoppiamento dei piani contribuisce alla stabilità dell’impedenza di alimentazione. Una bassa impedenza del sistema di distribuzione dell’alimentazione (PDN) è essenziale per minimizzare il rumore di commutazione simultanea (SSN), un fenomeno che diventa critico con l’aumento delle velocità di transizione e del numero di buffer commutanti.

Applicazione pratica: Riduzione del rumore in un FPGA ad alte prestazioni

In un sistema basato su FPGA operante a 500 MHz, l’ottimizzazione dell’accoppiamento tra piani ha permesso di ridurre significativamente il rumore di alimentazione. Il progettista ha implementato:

- Riduzione dello spessore del dielettrico tra piani di alimentazione e massa a 100 μm

- Utilizzo di materiale con εr = 4.5 per aumentare la capacità distribuita

- Segmentazione strategica dei piani di alimentazione con minime interruzioni

- Rete di condensatori di bypass progettata considerando la capacità distribuita intrinseca

Questa strategia ha permesso di ridurre l’impedenza del PDN sotto i 50 mΩ nella banda critica (10 MHz – 1 GHz), migliorando significativamente l’integrità del segnale e riducendo le emissioni EMI di 12 dB rispetto al design precedente.

Impedenza controllata

Per segnali ad alta velocità, è essenziale mantenere un’impedenza caratteristica costante lungo tutto il percorso. Il controllo dell’impedenza dipende da:

- Larghezza della traccia

- Spessore del rame

- Distanza dal piano di riferimento

- Costante dielettrica del substrato

CALCOLO DELL’IMPEDENZA CARATTERISTICA DI UNA TRACCIA

Per una microstriscia (microstrip):

Z₀ = (87 / √(εᵣ + 1.41)) × ln(5.98 × h / (0.8 × w + t))

Dove:

- Z₀ = impedenza caratteristica in Ohm

- εᵣ = costante dielettrica relativa del substrato

- h = altezza dal piano di riferimento

- w = larghezza della traccia

- t = spessore del rame

Per una stripline, la formula diventa più complessa:

Z₀ = (60 / √εᵣ) × ln(4h / (0.67 × π × (0.8w + t)))

Dove:

- h = distanza tra i piani di riferimento

- w = larghezza della traccia

- t = spessore del rame

Queste formule forniscono approssimazioni utili per stime preliminari, ma per calcoli precisi è raccomandabile utilizzare simulatori elettromagnetici o i tool di calcolo forniti dai produttori di PCB, che considerano anche effetti secondari come la rugosità del rame e le proprietà disperdenti del materiale.

L’impedenza caratteristica rappresenta una proprietà fondamentale delle linee di trasmissione nei PCB, e la sua gestione va ben oltre la semplice specifica di una larghezza di traccia. Un’impedenza non controllata o mal progettata causa riflessioni che degradano l’integrità del segnale, creando effetti come ringing, overshoot e jitter temporale.

Nella progettazione pratica, il controllo dell’impedenza richiede una stretta collaborazione con il produttore di PCB. Le tolleranze di produzione, in particolare quelle relative a spessore del rame e del dielettrico, influenzano direttamente l’impedenza risultante. Un progetto robusto dovrebbe considerare queste variazioni, implementando un margine di sicurezza adeguato.

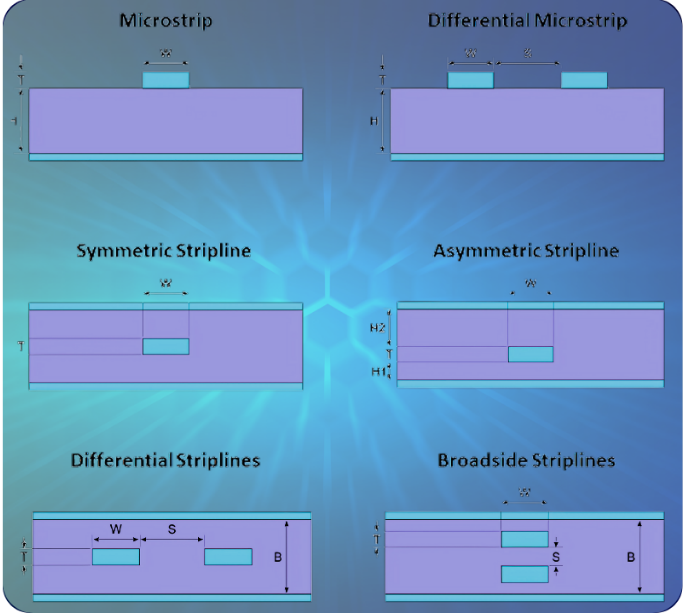

Le strutture di trasmissione più comuni nei PCB multi-layer sono:

- Microstrip: tracce sul layer esterno con un singolo piano di riferimento

- Stripline: tracce su layer interno tra due piani di riferimento

- Dual stripline: due layer di segnale condividono gli stessi piani di riferimento

- Asimmetric stripline: simile alla stripline ma con distanze diverse dai piani di riferimento

Ogni configurazione presenta vantaggi specifici in termini di prestazioni, densità di routing e facilità di produzione. La scelta della struttura ottimale dipende dai requisiti specifici del segnale e dai vincoli del progetto complessivo.

Applicazione: Interfaccia DDR4 ad alta velocità

In un sistema di elaborazione avanzato con memoria DDR4-3200, il controllo dell’impedenza si è rivelato cruciale per garantire l’integrità del segnale a 1600 MHz. Il progettista ha implementato:

- Tracce differenziali da 100 Ω (±5%) per segnali DQS

- Tracce single-ended da 50 Ω (±5%) per segnali DQ e comando

- Microstrip sugli strati esterni per facilitare la terminazione

- Stripline nei layer interni per segnali critici con minore tolleranza alla diafonia

Il processo ha incluso:

- Simulazione preliminare con diversi stackup e geometrie

- Collaborazione con il produttore per definire parametri realizzabili

- Realizzazione di coupon di test sul pannello di produzione

- Verifica dell’impedenza mediante TDR (Time Domain Reflectometry)

Questa attenzione al controllo dell’impedenza ha permesso di ottenere un margine di timing superiore al 10% rispetto ai requisiti minimi, garantendo operazioni affidabili anche in condizioni ambientali variabili.

Distribuzione dei segnali critici

I segnali ad alta velocità o sensibili dovrebbero essere:

- Posizionati vicino a piani di riferimento continui

- Separati da segnali potenzialmente interferenti

- Distribuiti su layer interni quando possibile

- Raggruppati per tipo e frequenza

La distribuzione ottimale dei segnali all’interno dello stackup rappresenta una delle sfide più complesse nella progettazione di PCB avanzati. Ogni decisione di posizionamento influenza non solo le prestazioni del singolo segnale, ma l’intero ecosistema elettromagnetico del circuito.

Un principio fondamentale è la segregazione per domini funzionali e di frequenza. I segnali analogici a bassa frequenza, quelli digitali veloci e i circuiti di potenza dovrebbero occupare aree distinte del PCB, con confini ben definiti. Questa separazione si estende anche verticalmente attraverso lo stackup, con layer dedicati a specifiche categorie di segnali.

Per i segnali ad alta velocità, la distribuzione deve considerare anche i percorsi di ritorno della corrente. Secondo la teoria della linea di trasmissione, la corrente di ritorno segue il percorso a minima impedenza, che alle alte frequenze coincide con l’area direttamente sotto la traccia. Interruzioni in questo percorso (slot nei piani, cambi di piano di riferimento) generano loop di corrente estesi che aumentano emissioni e suscettibilità.

La distribuzione dovrebbe anche minimizzare i percorsi critici. Segnali di clock, reset e controlli sincroni meritano particolare attenzione, con routing ottimizzato per minimizzare lunghezza e skew. Tecniche come “length matching” e “delay tuning” diventano essenziali per garantire tempistiche corrette in sistemi ad alta velocità.

Applicazione pratica: Sistema di acquisizione immagini medicale

In un sistema di imaging medicale di precisione, la distribuzione dei segnali è stata ottimizzata per garantire integrità del segnale e minimizzare interferenze:

- Segnali analogici dei sensori instradati esclusivamente su layer 3, schermato da due piani di massa

- Linee di clock ad alta frequenza (125 MHz) isolate su layer 6 con guard traces ai lati

- Bus di dati ad alta velocità distribuiti su layer 4 e 5 come stripline differenziali

- Circuiti di alimentazione switching confinati in un’area dedicata del PCB con schermatura locale

Per i segnali più critici, il progettista ha implementato:

- Riferimenti di tensione analogici tracciati come “star topology” per minimizzare interferenze

- Critical nets identificate e simulate individualmente con analisi di integrità del segnale

- Via shielding attraverso strutture a “picket fence” per transizioni tra layer

- Topologia a “H-tree” per la distribuzione del clock principale

Queste strategie hanno permesso di raggiungere un rapporto segnale/rumore superiore a 90 dB nei circuiti analogici, essenziale per l’accuratezza diagnostica del sistema, pur mantenendo emissioni EMI ben al di sotto dei limiti normativi per dispositivi medicali.

Conclusione

La progettazione dello stackup rappresenta una decisione architettonica fondamentale che influenza l’intero ciclo di vita di un prodotto elettronico. Una disposizione ottimale dei layer bilancia requisiti elettrici, termici, meccanici ed economici, offrendo un vantaggio competitivo in termini di prestazioni, affidabilità e time-to-market.

Lo stackup non è semplicemente un aspetto tecnico della progettazione, ma una decisione strategica che definisce le capacità e i limiti fondamentali di un sistema elettronico. La crescente complessità dei dispositivi moderni, con la loro integrazione di tecnologie diverse (digitale, analogica, RF, potenza) in spazi sempre più ridotti, rende questa decisione architetturale ancora più critica.

L’approccio ottimale alla progettazione dello stackup richiede una visione olistica che integri prospettive diverse: le esigenze elettriche di integrità del segnale e compatibilità elettromagnetica, i requisiti termici per la dissipazione efficiente del calore, i vincoli meccanici per resistenza e stabilità, e le considerazioni economiche relative a costi e producibilità.

Per i progettisti, è essenziale considerare lo stackup nelle prime fasi del processo di sviluppo, collaborando strettamente con i produttori di PCB per garantire fattibilità e ottimizzazione dei costi. Per i decision-maker, comprendere l’impatto dello stackup sulle prestazioni del prodotto finale consente di allocare adeguatamente risorse e definire specifiche realistiche.

I principi fondamentali presentati in questo articolo – simmetria, segmentazione appropriata, controllo dell’impedenza, e distribuzione ottimale dei segnali – forniscono una base solida per affrontare questa sfida progettuale. Tuttavia, ogni applicazione presenta caratteristiche uniche che richiedono considerazioni specifiche e, spesso, compromessi ponderati.

In un contesto tecnologico in continua evoluzione, la capacità di progettare stackup ottimizzati diventa una competenza strategica che differenzia prodotti eccellenti da quelli mediocri. Le aziende che investono in questa competenza possono ottenere vantaggi significativi in termini di qualità, costi e velocità di sviluppo.

Le tendenze emergenti nei materiali e nelle tecnologie di interconnessione promettono di espandere ulteriormente le possibilità, consentendo prestazioni sempre più elevate in spazi sempre più ridotti. I progettisti che comprendono a fondo i principi fondamentali dello stackup saranno meglio equipaggiati per sfruttare queste innovazioni e sviluppare la prossima generazione di prodotti elettronici.

Nella Parte 2 di questa guida ci addentreremo nelle considerazioni economiche da effettuare prima di decidere quale stackup adottare, in modo da non tenere in considerazione solo il costo del PCB ma il cossiddetto TOC (Total Cost of Ownership) del prodotto. Vedremo un’altra carrellata di esempi applicativi e le tendenze evolutive degli stackup grazie all’avanzamento della tecnologia.

Continuate a seguirci!